# Technische Informatik 1

**Prof. Dr. Rolf Drechsler**

**Christina Plump**

# Überblick

## Teil 1: Der Rechneraufbau (Kapitel 2-5)

- Rechner im Überblick

- Pipelining

- Speicher

- Parallelverarbeitung

## Teil 2: Der Funktionalitätsaufbau (Kapitel 6-12)

- Kodierung

- Grundbegriffe, Boolesche Funktionen

- Darstellungsmöglichkeiten

- **Schaltkreise, Synthese, spezielle Schaltkreise**

- Addierer, Inkrementer

- **Subtrahierer, Multiplizierer, ALU**

# Kapitel 11: Arithmetische Schaltkreise

Addierer, Multiplexer und Inkrementer

Subtrahierer, Multiplizierer und ALU

# Subtrahierer im Allgemeinen

## Gegeben:

Zwei Binärzahlen  $a = a_{n-1} \dots a_0$ ,  $b = b_{n-1} \dots b_0$

## Gesucht:

Schaltkreis, der Binärdarstellung  $s$  mit  $\langle s \rangle = \langle a \rangle - \langle b \rangle$  berechnet.

## Bemerkung:

- Wegen  $-[b]_2 = \bar{b} + 1$ , gilt  $[a]_2 - [b]_2 = [a]_2 + \bar{b}_2 + 1$ .

- Rückführung eines Subtrahierers auf einen Addierer

- Bau kombinierter Addierer/Subtrahierer Schaltkreise

## Bespiel und Schaltbild eines Subtrahierers

$$[a] = [0110] = 6_{10}, \quad [b] = [0111] = 7_{10}, \quad [\bar{b}] = [1000]$$

$$\begin{array}{r}

0100 \\

1000 \\

\hline

1

\end{array}

\quad

\begin{array}{r}

6_{10} \\

-7_{10} \\

\hline

-1_{10}

\end{array}$$

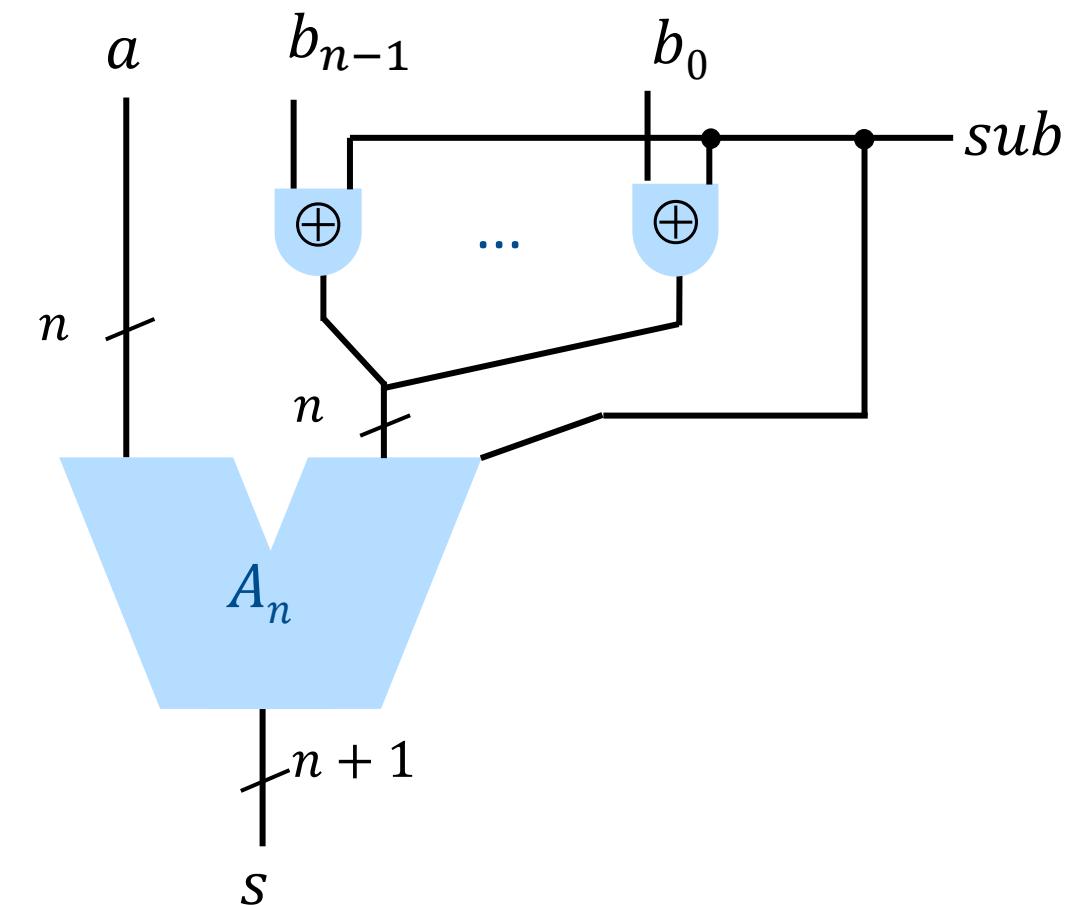

## Schaltbild für einen Addierer/Subtrahierer

- Erinnerung:

$$\begin{aligned}-b_i \oplus 0 &= b_i \\ -b_i \oplus 1 &= \overline{b_i}\end{aligned}$$

- Verhalten für Belegungen von  $sub$ :

$$\begin{aligned}-sub = 0: [a]_2 + [b]_2 + 0 &= [a]_2 + [b]_2 \\ -sub = 1: [a]_2 + [\overline{b}]_2 + 1 &= [a]_2 - [b]_2\end{aligned}$$

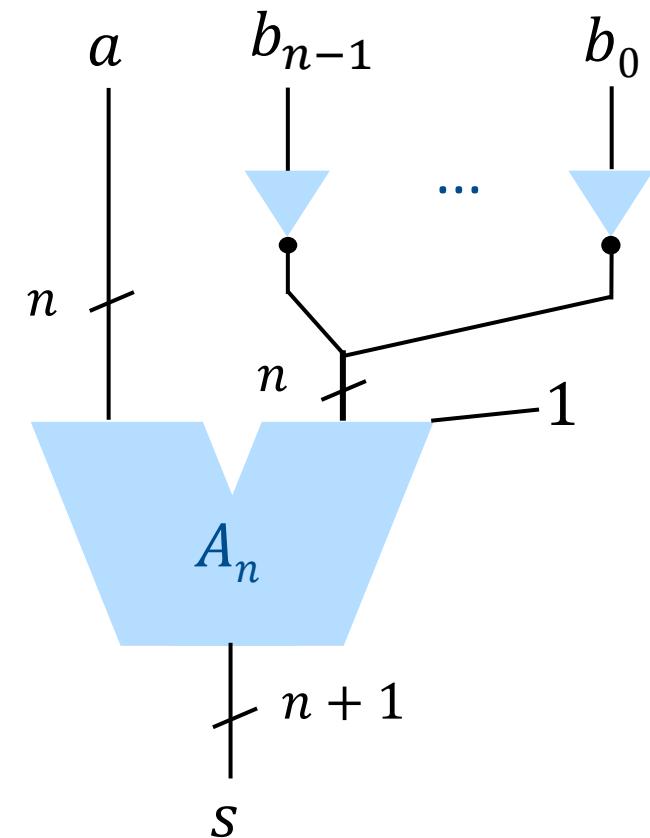

# Multiplizierer im Allgemeinen

## Gegeben:

- Zwei Binärzahlen  $a = a_{n-1} \dots a_0$ ,  $b = b_{n-1} \dots b_0$

## Gesucht:

Schaltkreis, der Binärdarstellung  $s$  mit  $\langle s \rangle = \langle a \rangle \cdot \langle b \rangle$  berechnet.

## Bemerkung:

- Wegen  $\langle a \rangle \cdot \langle b \rangle \leq (2^{n-1} - 1) \cdot (2^{n-1} - 1) = 2^{2n} - 2^{n+1} + 1 \leq 2^{2n} - 1$ , genügen  $2n$  Bits für die Darstellung von  $s$ , d.h. als Ausgang des Schaltkreises.

- Da sich die Multiplikation vorzeichenbehafteter Binärzahlen auf die Multiplikation positiver Binärzahlen zurückführen lässt (Vorzeichen wird getrennt berechnet), reicht die Betrachtung positiver Binärzahlen aus.

## Multiplizierer im Allgemeinen (2)

### Definition ( $n$ -Bit Multiplizierer):

Ein  $n$ -Bit Multiplizierer ist ein Schaltkreis, der die folgende Boolesche Funktion  $\cdot_n$  berechnet:

$$\begin{aligned}\cdot_n: \mathbb{B}^{2n} &\rightarrow \mathbb{B}^{2n} \\ (a_{n-1}, \dots, a_0, b_{n-1}, \dots, b_0) &\mapsto (p_{2n-1}, \dots, p_0),\end{aligned}$$

sodass  $\langle p \rangle = \langle a \rangle \cdot \langle b \rangle$  gilt.

### Beispiel:

$$6_{10} \cdot 5_{10} = (110)_2 \cdot (101)_2 = (11110)_2 = 30_{10}$$

$$\begin{array}{r} 1 & 1 & 0 & \cdot & 1 & 0 & 1 \\ \hline & 1 & 1 & 0 \\ & 0 & 0 & 0 \\ \hline & 1 & 1 & 0 \\ \hline 1 & 1 & 1 & 1 & 0 \end{array}$$

## Berechnung der Partialprodukte (Multiplikationsmatrix)

- Multiplikationsmatrix beinhaltet Partialprodukte

- Realisierung der Multiplikationsmatrix mit  $n^2$  AND-Gattern und  $n^2$  Konstanten 0.

$$\begin{pmatrix} pp_0 \\ pp_1 \\ \vdots \\ pp_{n-1} \end{pmatrix} = \begin{pmatrix} 0 & 0 & \dots & 0 & 0 & a_{n-1}b_0 & a_{n-2}b_0 & \dots & a_1b_0 & a_0b_0 \\ 0 & 0 & \dots & 0 & a_{n-1}b_1 & a_{n-2}b_1 & a_{n-3}b_1 & \dots & a_0b_1 & 0 \\ \vdots & & & & \vdots & \vdots & \vdots & & & \vdots \\ 0 & a_{n-1}b_{n-1} & \dots & a_2b_{n-1} & a_1b_{n-1} & a_0b_{n-1} & 0 & & 0 & 0 \end{pmatrix}$$

## Notwendig zur Berechnung der Multiplikation

- Schnelle Addition von  $n$  Partialprodukten der Länge  $2n$

- Mit CLAs lösbar mit

- Kosten:  $\mathcal{O}(n^2)$

- Tiefe: Unterscheide die Art der Aufsummierung:

- Lineares Aufsummieren:  $\mathcal{O}(n \log n)$

- Baumartiges Aufsummieren:  $\mathcal{O}(\log^2 n)$

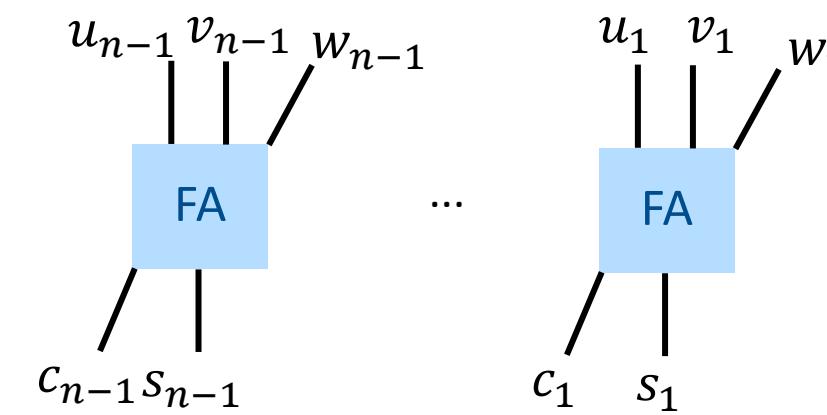

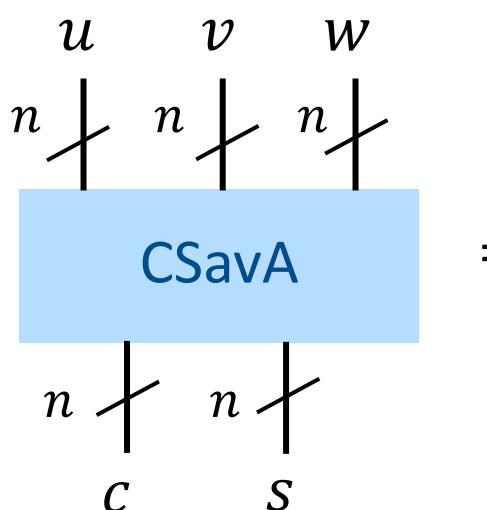

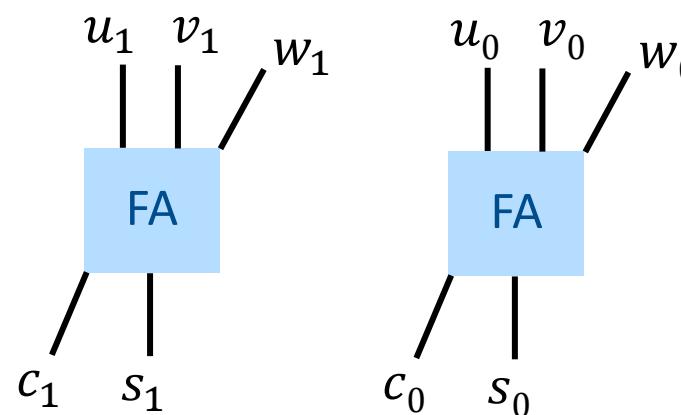

## Schnelleres Summieren: Carry-Save Addierer

- Verbesserbar durch Carry-Save Addierer

- Reduziert drei Eingabewerte zu zwei Ausgabewerten

- Lösbar durch Hintereinandersetzen von Volladdierern, d.h. keine Carry Chain

$$\langle u \rangle + \langle v \rangle + \langle w \rangle = \langle c \rangle + \langle s \rangle$$

$$\begin{array}{r}

u_{n-1} \quad u_{n-2} \quad \dots \quad u_2 \quad u_1 \quad u_0 \\

v_{n-1} \quad v_{n-2} \quad \dots \quad v_2 \quad v_1 \quad v_0 \\

w_{n-1} \quad w_{n-2} \quad \dots \quad w_2 \quad w_1 \quad w_0 \\

\hline

c_{n-1} \quad c_{n-2} \quad \dots \quad c_1 \quad c_0 \quad 0 \\

0 \quad s_{n-1} \quad s_{n-2} \quad \dots \quad s_2 \quad s_1 \quad s_0

\end{array}$$

Nutzung für Partialprodukte!

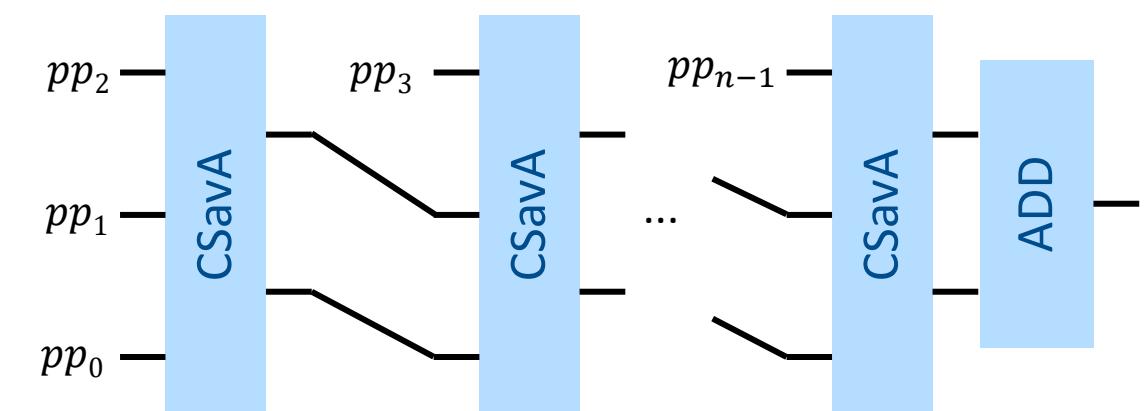

## 1. Serielle Lösung:

- Hintereinanderschalten von  $(n - 2)$  CSavA-Addierern der Länge  $2n$

- Fasse  $n$  Partialprodukte zu zwei  $2n$ -Bit-Worten zusammen

- Addiere die  $2n$ -Bit-Worte mit CLA

- **Kosten:**  $\mathcal{O}(n^2)$

- **Tiefe:**  $\mathcal{O}(n)$

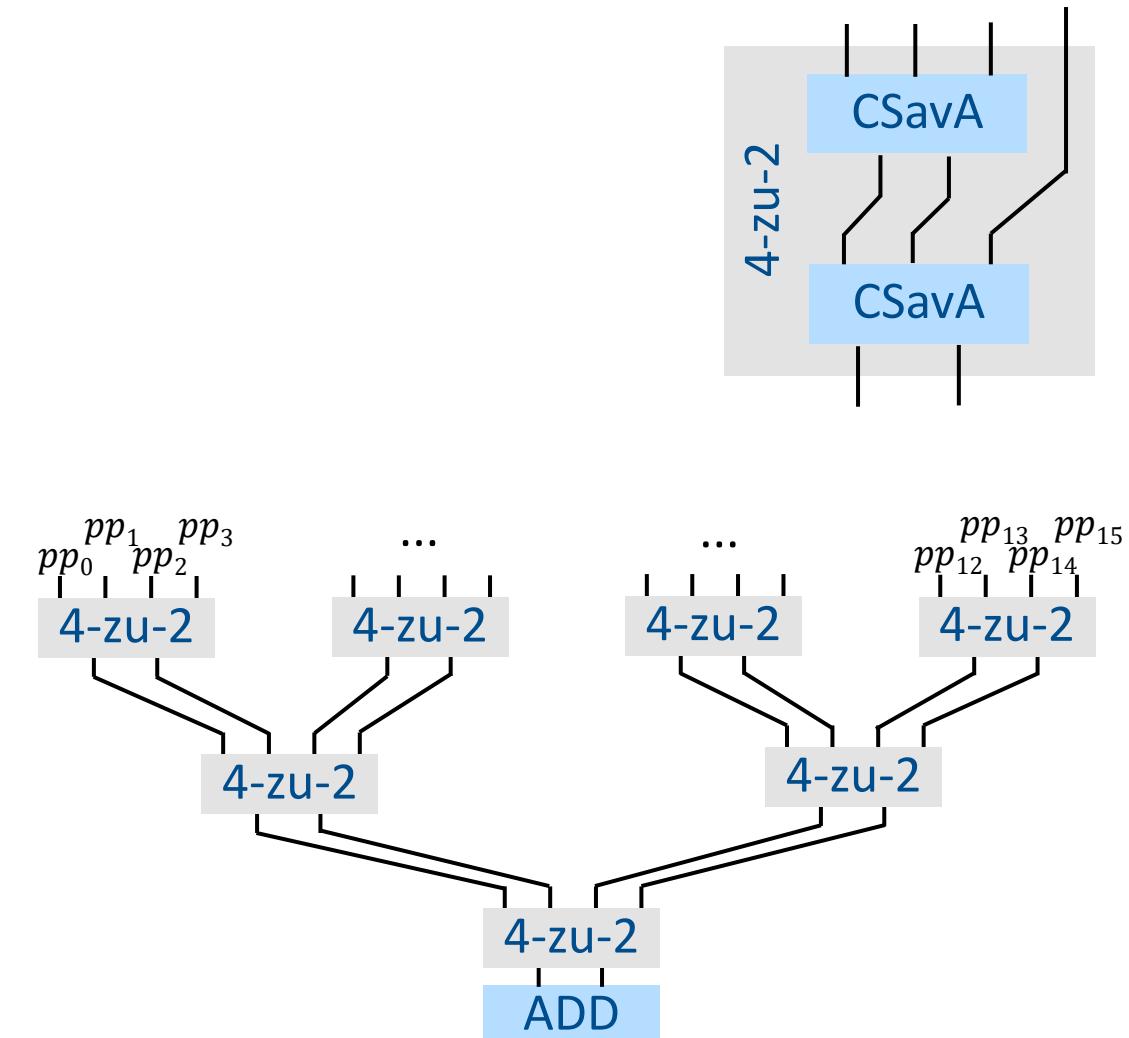

## 2. Baumartige Lösung:

- Neue Grundzelle (4-zu-2) zur Reduktion von vier  $2n$ -Bit Eingabeworten zu zwei Ausgabeworten, bestehend aus zwei CSavA

- Baumartiges Zusammenfassen der Partialprodukte mit 4-zu-2-Bausteinen zu zwei  $2n$ -Bit-Worten

- Addiere die  $2n$ -Bit-Worte mit CLA

- **Kosten:**  $\mathcal{O}(n^2)$

- **Tiefe:**  $\mathcal{O}(\log n)$

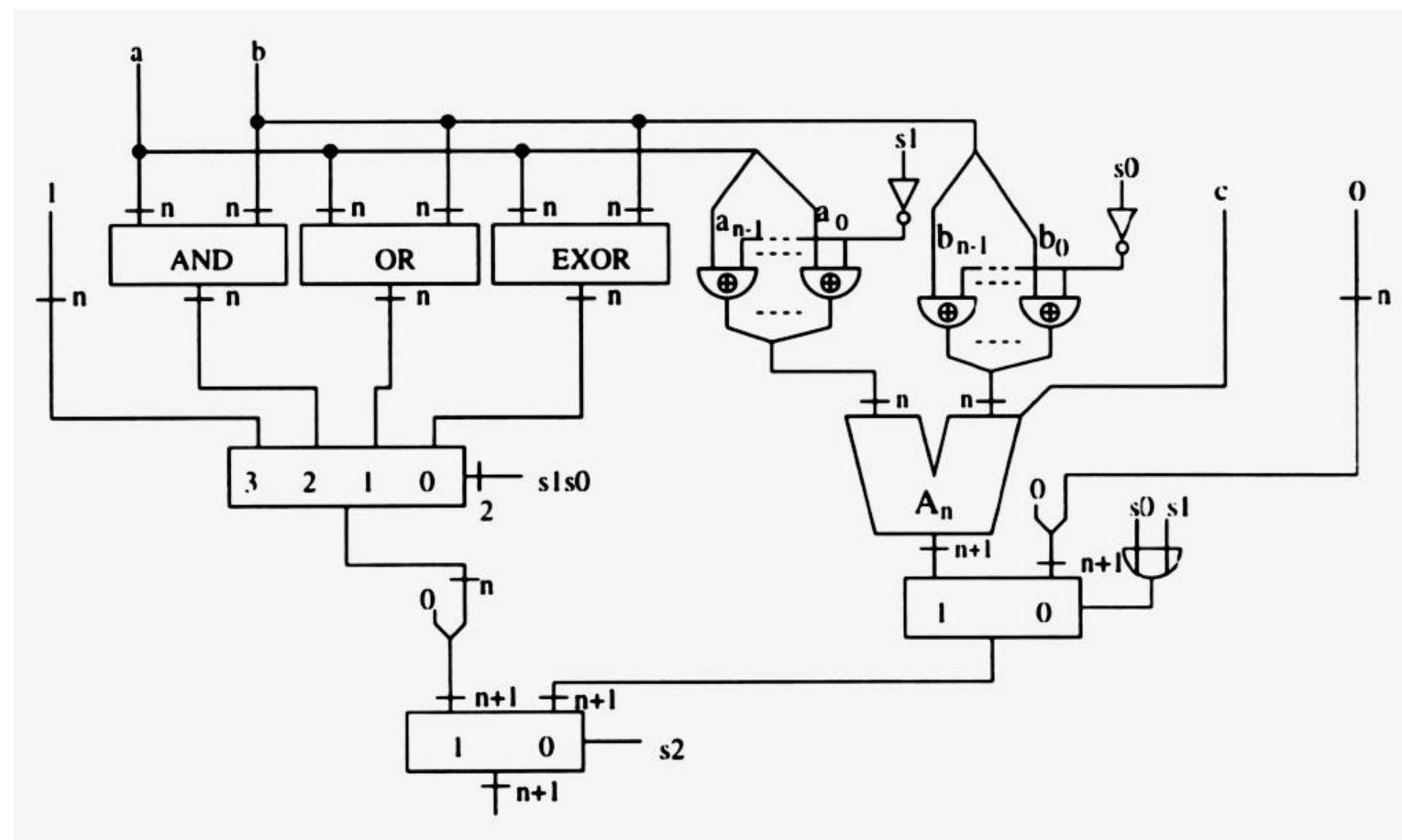

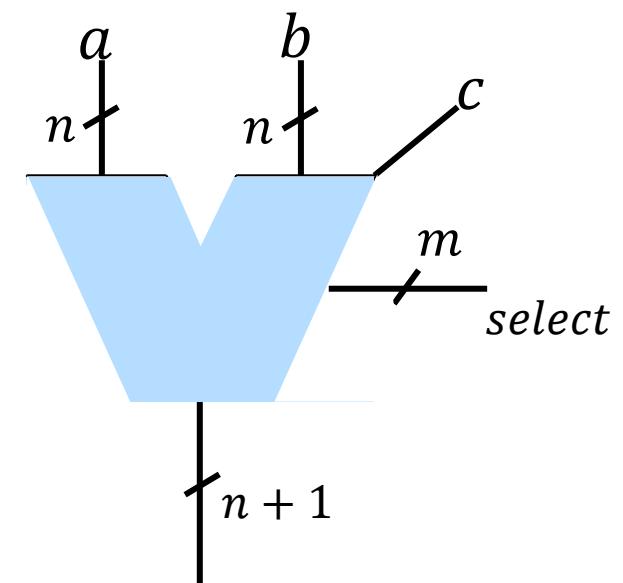

# Aufbau einer ALU

## Definition (n-Bit ALU):

Eine  $n$ -bit Arithmetic Logic Unit (ALU) ist ein Schaltkreis zur Berechnung von arithmetischen und logischen Funktionen mit

- zwei  $n$ -Bit Operanden  $a, b$ ,

- einem Eingangsübertrag  $c$

- einem  $m$ -Bit select Eingang, der die auszuführende Funktion auswählt

- einem  $n + 1$  -Bit Ausgang  $s$

## Aufbau einer ALU (2)

Beispiel für ALU mit acht Funktionen: 3-bit *select*-Eingang

| Funktionsnr.              | ALU-Funktion                                                   |

|---------------------------|----------------------------------------------------------------|

| $s_2 \quad s_1 \quad s_0$ |                                                                |

| 0 0 0                     | $(0, \dots, 0)$                                                |

| 0 0 1                     | $[b]_2 - [a]_2$                                                |

| 0 1 0                     | $[a]_2 - [b]_2$                                                |

| 0 1 1                     | $[a] + [b] + c$                                                |

| 1 0 0                     | $a \oplus b = (a_{n-1} \oplus b_{n-1}, \dots, a_0 \oplus b_0)$ |

| 1 0 1                     | $a + b = (a_{n-1} + b_{n-1}, \dots, a_0 + b_0)$                |

| 1 1 0                     | $a \cdot b = (a_{n-1} \cdot b_{n-1}, \dots, a_0 \cdot b_0)$    |

| 1 1 1                     | $(1, \dots, 1)$                                                |

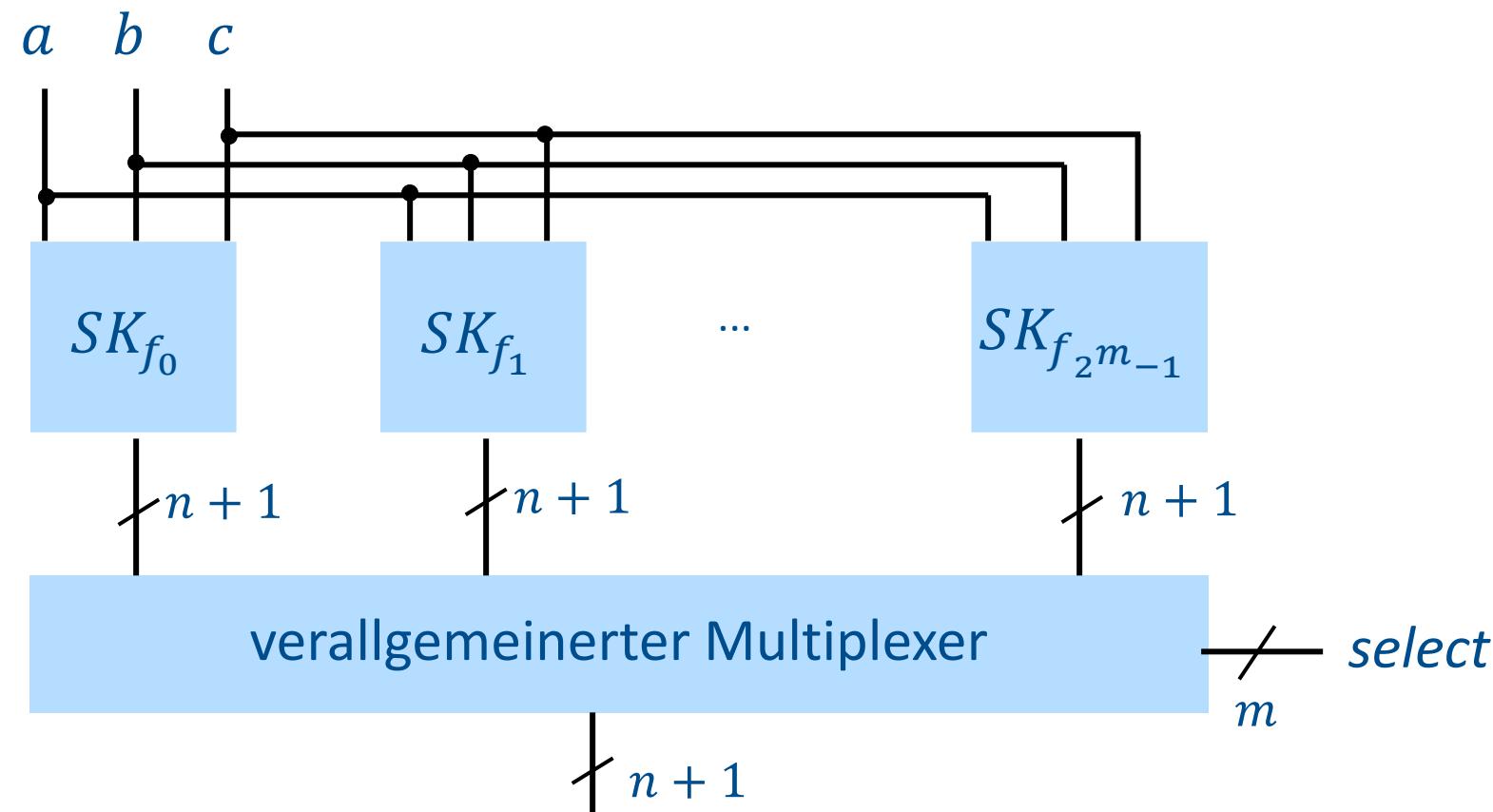

# Mögliche Realisierungen einer ALU

## Getrennte Schaltkreise

- Realisiere  $2^m - 1$  unterschiedliche Funktionen  $f_0, \dots, f_{2^m-1}$  durch getrennte Schaltkreise  $SK_i$

- Wähle Funktion durch verallgemeinerten Multiplexer (siehe nächste Folie)

## Gemeinsamer Schaltkreis

- Entwirf Schaltkreis mit gemeinsamer Behandlung ähnlicher Funktionen

- Beispiel auf übernächster Folie

## Realisierung der $n$ -Bit-ALU (Einzelfunktionen getrennt)

# Schaltungsrealisierung der $n$ -Bit-ALU mit Überlappung von Einzelfunktionen