# Technische Informatik 1

**Prof. Dr. Rolf Drechsler**

**Christina Plump**

# Überblick

## Teil 1: Der Rechneraufbau (Kapitel 2-5)

- Rechner im Überblick

- Pipelining

- Speicher

- Parallelverarbeitung

## Teil 2: Der Funktionalitätsaufbau (Kapitel 6-12)

- **Kodierung**

- Zeichen

- Zahlen

- Grundbegriffe, Boolesche Funktionen

- Darstellungsmöglichkeiten

- Schaltkreise, Synthese, spezielle Schaltkreise

# Kapitel 12: Realisierung digitaler Bausteine

Transistoren

Logische Gatter

Flip Flops

1-Bit Speicherzelle

# Unterschiede zwischen analogen und digitalen Schaltkreisen

| Analoger Schaltkreis                                 | Idealer digitaler Schaltkreis |

|------------------------------------------------------|-------------------------------|

| kontinuierlicher Wertebereich                        | diskreter Wertebereich        |

| Laufzeiteffekte,<br>kein eindeutiger Schaltzeitpunkt | verzögerungsfrei              |

| Eingangsstrom/-spannung;<br>Ausgangsstrom/-spannung  | Ein- und Ausgangswert         |

| Verlustleistung                                      | verlustfreie Berechnung       |

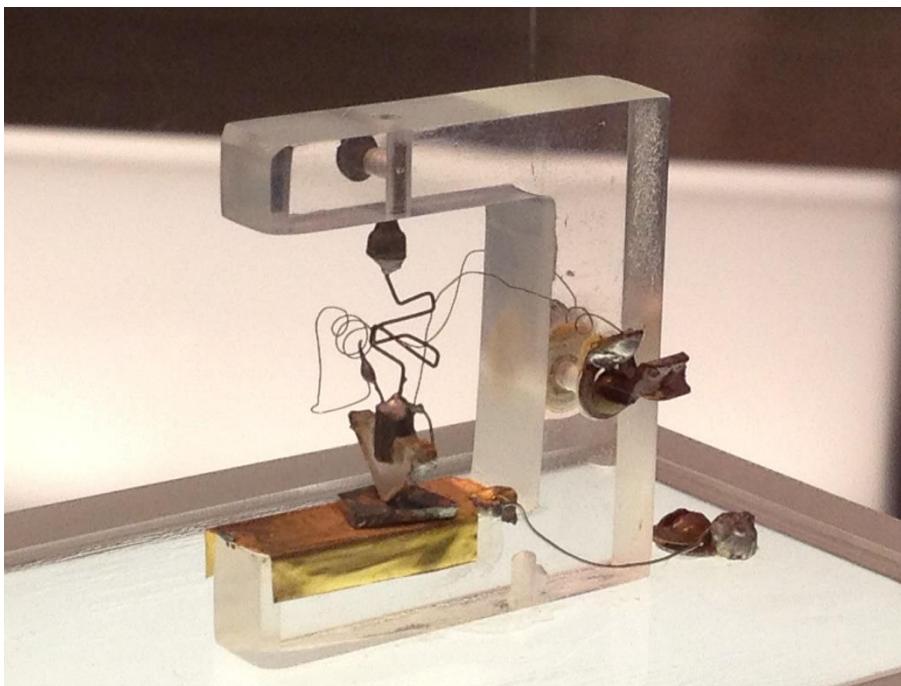

## Entwicklung / Bauform

## Aufbau: Diode (1)

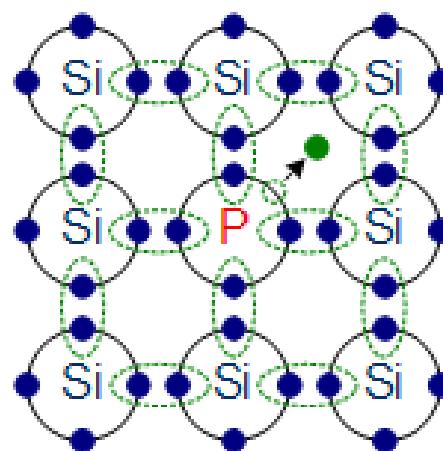

- Wie geht eigentlich Dotierung?

- Silizium, Gallium, Arsenid

- Bandlücken/Überschüssige Elektronen

Das Phosphor-Atom gibt sein 5. Elektron ab, das keine Bindung eingehen kann. Es dient als freier Ladungsträger.

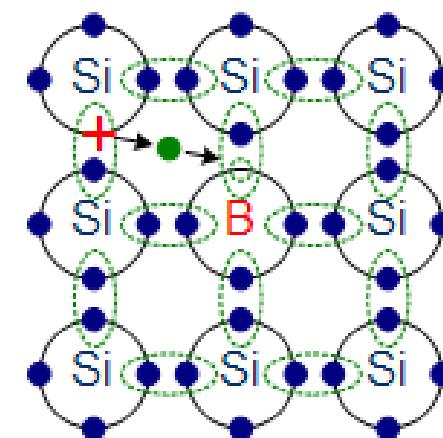

Die freie Stelle am Bor-Atom wird von anderen Elektronen aufgefüllt. Dabei entstehen an anderer Stelle neue Löcher. Diese Leerstellen wandern scheinbar entgegengesetzt zum Elektronenfluss

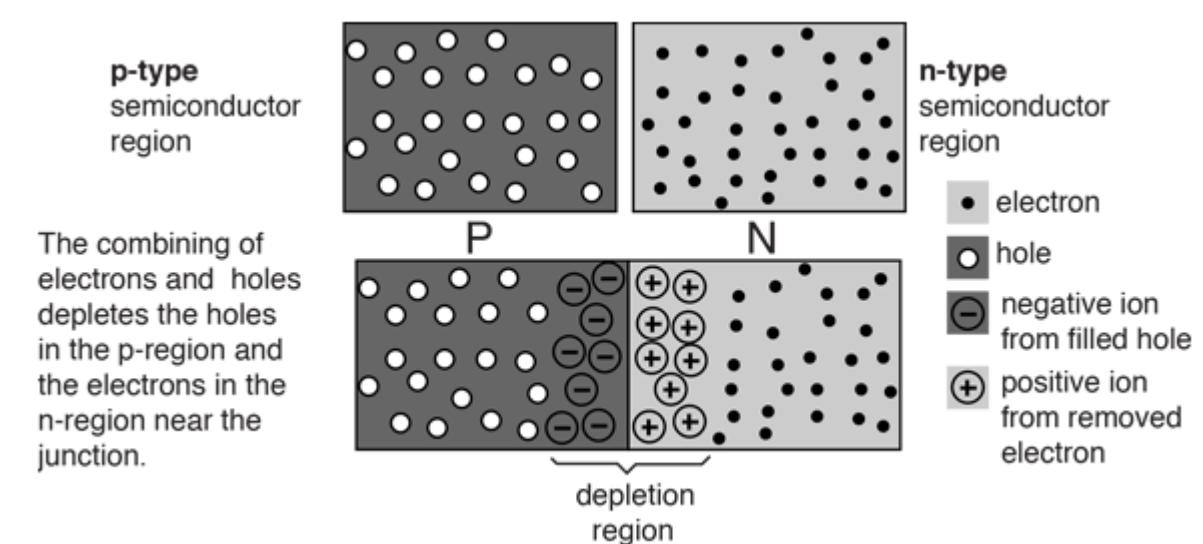

## Aufbau: Diode (2)

- P-N Übergang (Grenzfläche)

- Freie Elektronen rekombinieren mit P-Band Löchern

- Auffüllen eines Loches hinterlässt ein positives Ion

- Verarmungszone baut elektrisches Potential auf

- Geringe Leitfähigkeit

## Aufbau: Diode (3)

P-N Übergang (Grenzfläche)

- „Forward Bias“:

- *Positive* Spannung an P-Kanal anlegen, Negative an N-Kanal

- Elektronen gleichen Ionen in Sperrzone aus

- Strom fließt

- „Negative Bias“

- *Negative* Spannung an P-Kanal, Positive an N-Kanal

- Mehr freie Elektronen werden aus N-Kanal gezogen

- Sperrzone vergrößert sich

- Kein Strom fließt

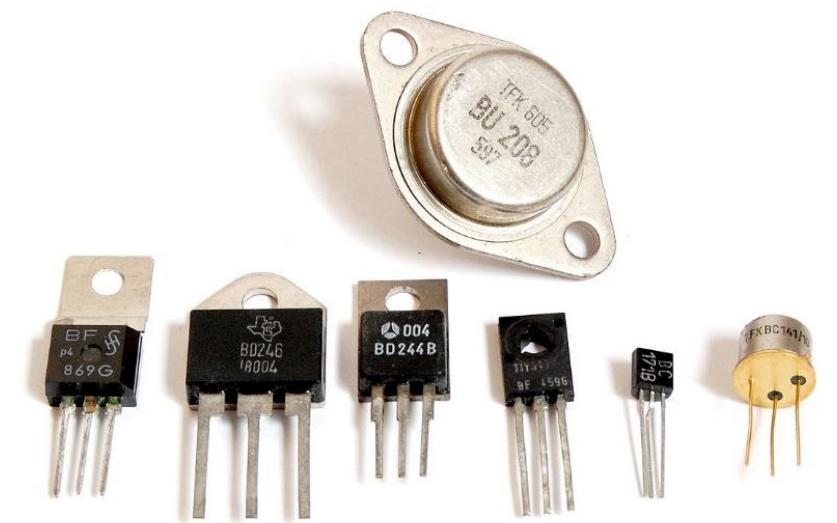

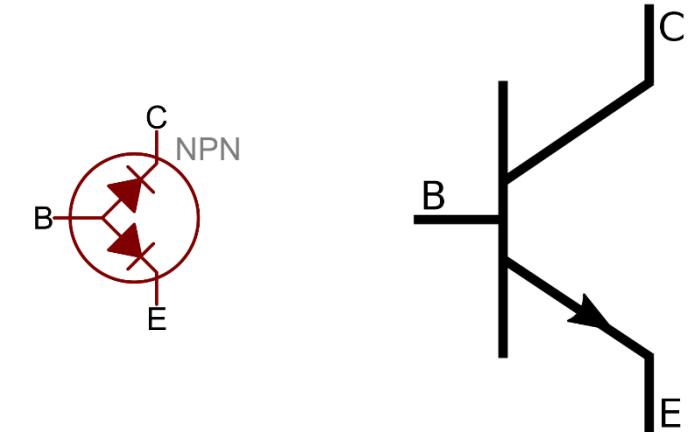

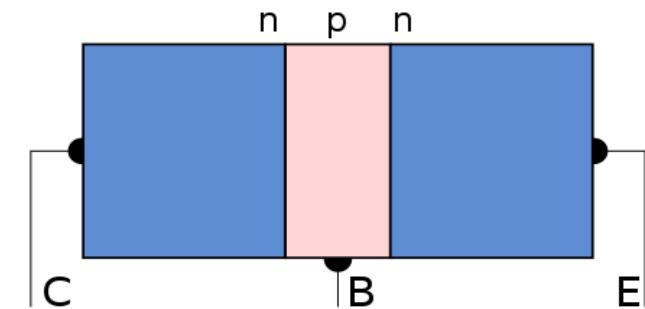

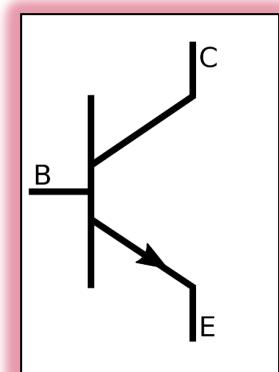

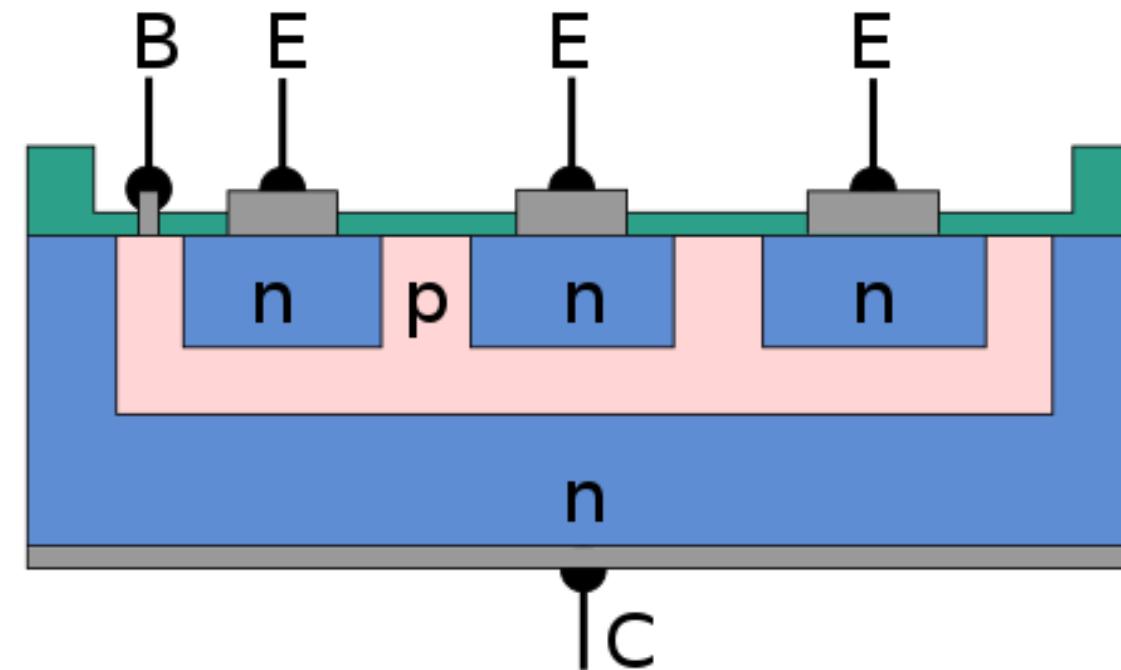

## Aufbau: Bipolarer Transistor

- Ein **bipolarer Transistor** besteht aus drei dotierten Bereichen, bezeichnet als

- Kollektor (C)

- Basis (B)

- Emitter (E)

- Zwei gegenläufige Dioden

- Es existieren bipolare *npn*-Transistoren (hier gezeigt) und *pnp*-Transistoren

- Neben der Bipolar- wird auch die Metalloxidschicht (MOS)-Technik verwendet

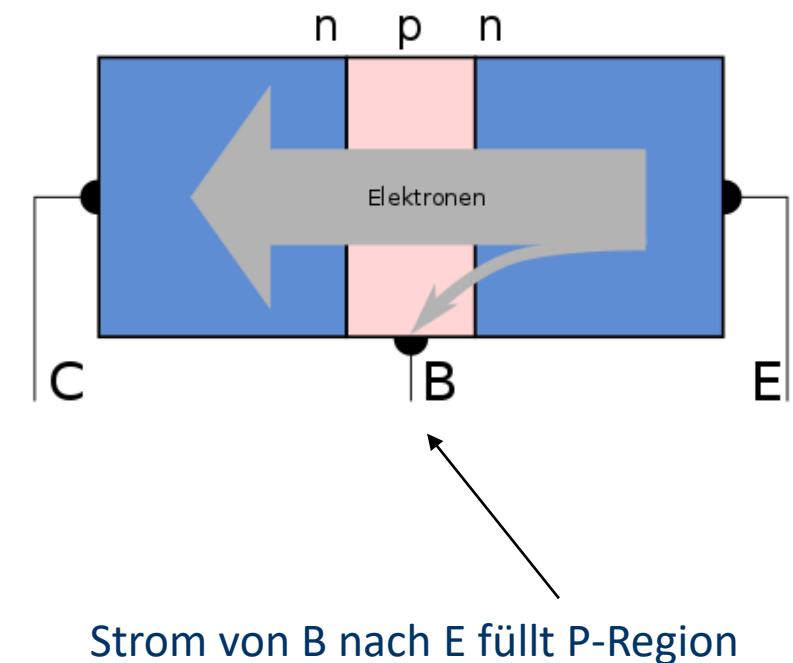

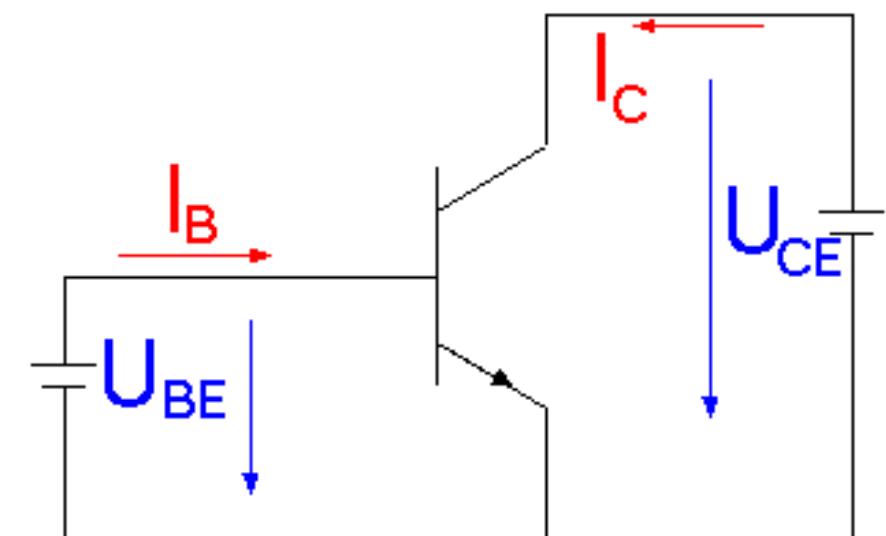

## Aufbau: Bipolarer Transistor

- Durch den „*Basis-Emitter-Strom*“ wird der Transistor für den Elektronenfluss von Emitter nach Kollektor leitend

- Ein vergleichsweise *kleiner* Basis-Emitter-Strom ( $I_{BE}$ ) kann einen vergleichsweise *großen* „*Emitter-Kollektor-Strom*“ ( $I_{EC}$ ) schalten

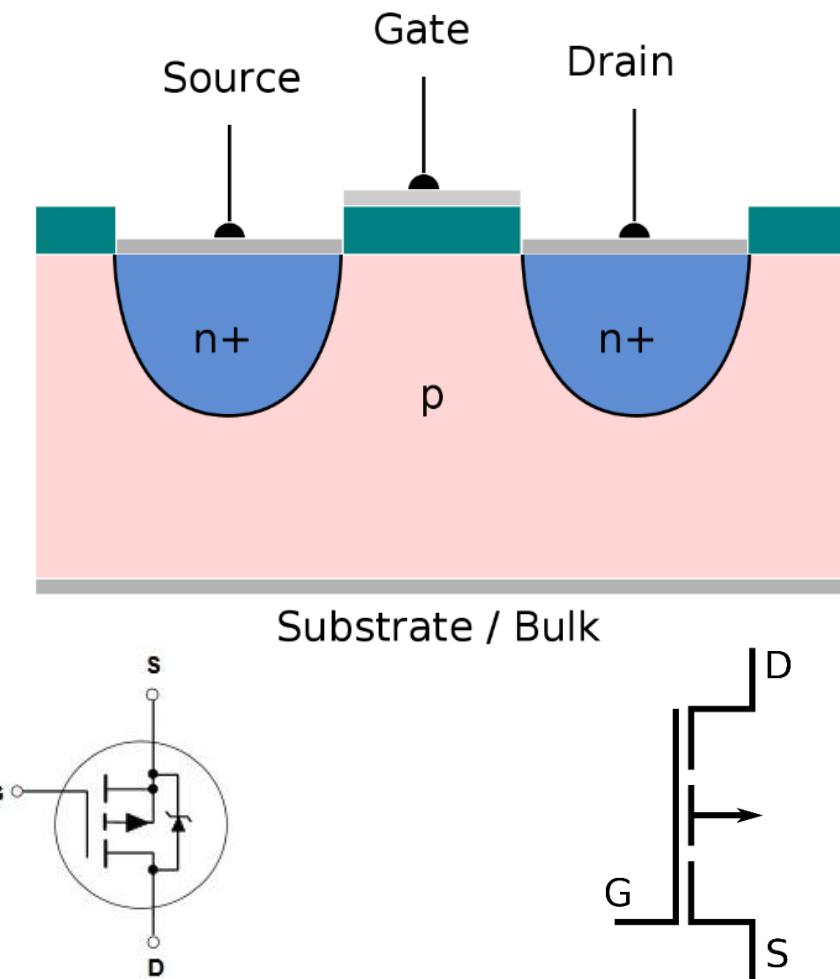

## Exkurs: Feldeffekttransistor

- Ein **Feldeffekttransistor (FET)** besteht aus drei dotierten Bereichen, bezeichnet als

- Source (S)

- Gate (G)

- Drain (D)

- Es existieren *N-Kanal* (wie hier gezeigt) und *P-Kanal* FETs (es gibt weitere Typen)

- Im Vgl. zu einem klassischen Transistor ist der FET *spannungsgesteuert*

- Weniger Verluste, höhere Verstärkung

- Kleinerer Arbeitsbereich

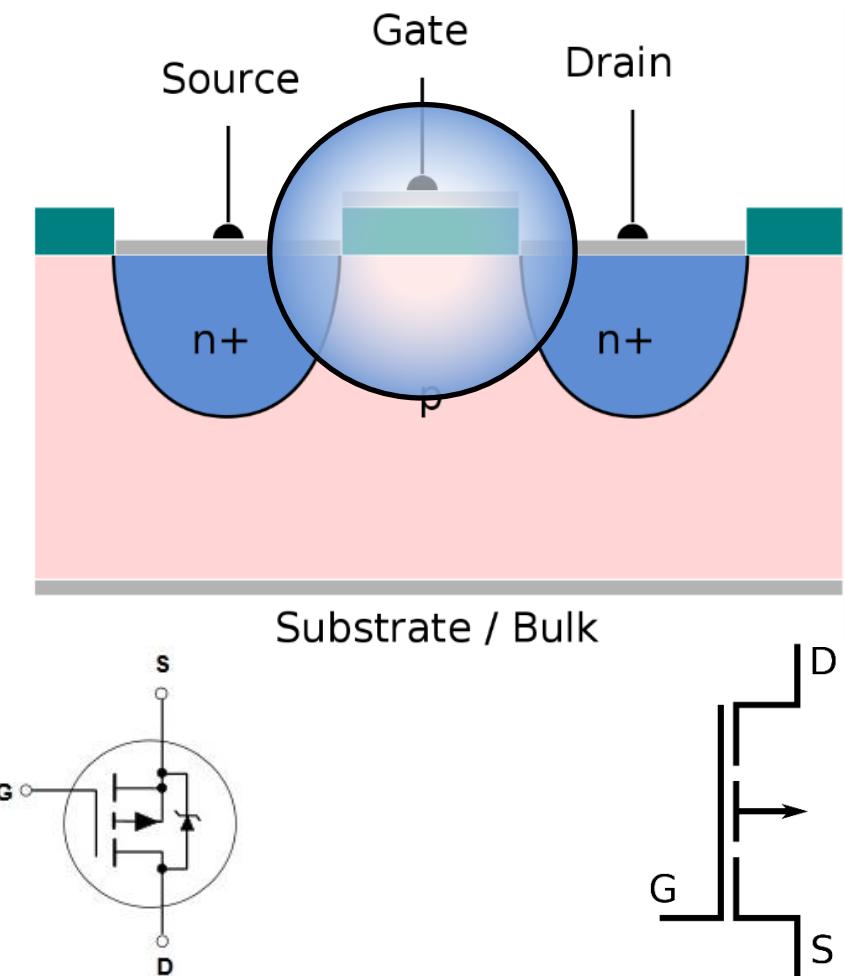

## Exkurs: Feldeffekttransistor

- Durch eine **Spannung**  $U_G$  am Gate bildet das dotierte Halbleitermaterial einen leitenden Kanal zwischen Source und Drain

- Mit einem FET kann durch eine Spannung ein großer Source-Drain-Strom geschaltet werden

- Strom spielt beim „Laden“ oder „Umladen“ des Gates eine Rolle

- I.d.R. herstellungsbedingt „Body-Diode“

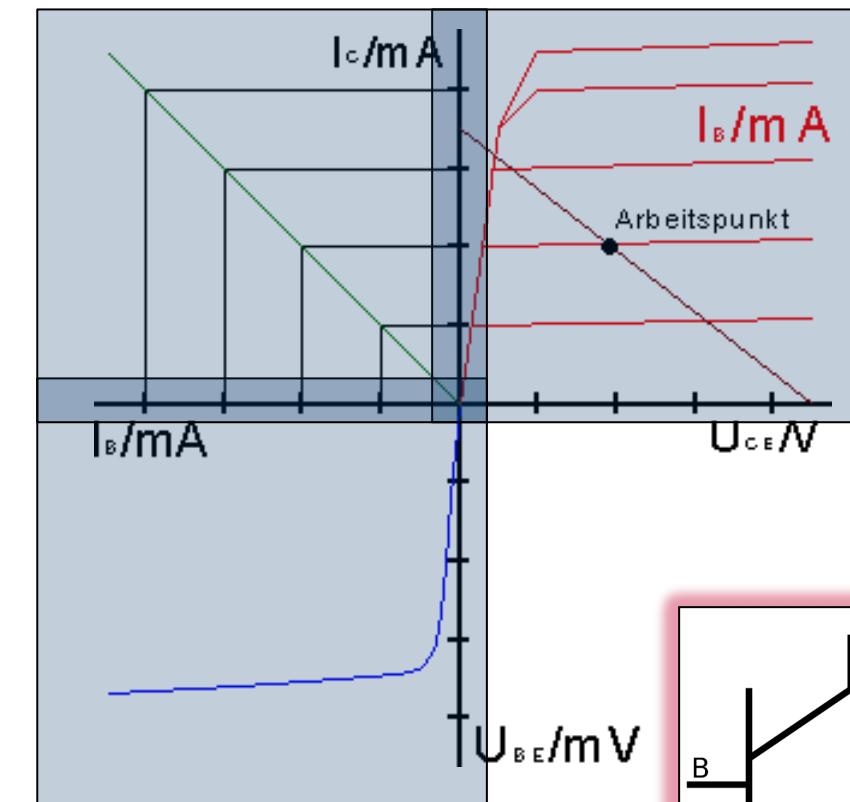

## Graphische Darstellung des Verhaltens

- Die Eigenschaften eines Transistors werden in einem Kennlinienfeld dargestellt

- Eingangskennlinienfeld

$I_B = f(U_{BE})$

- Ausgangskennlinienfeld

$I_C = f(U_{CE})$

- Steuerkennlinienfeld

$I_C = f(I_B)$

## Einsatz

- Als **Schalter**:

- $I_C$  fließt nur, wenn  $I_B$  fließt,

- $I_B$  fließt, wenn  $U_{BE} > 0,6V$

- Als **Verstärker**:

- $I_C$  ändert sich mit  $I_B$ ,

- $I_C = c \cdot I_B$ , solange  $U_{CE} > 4V$ ,  $c$  durch Bauweise bestimmt

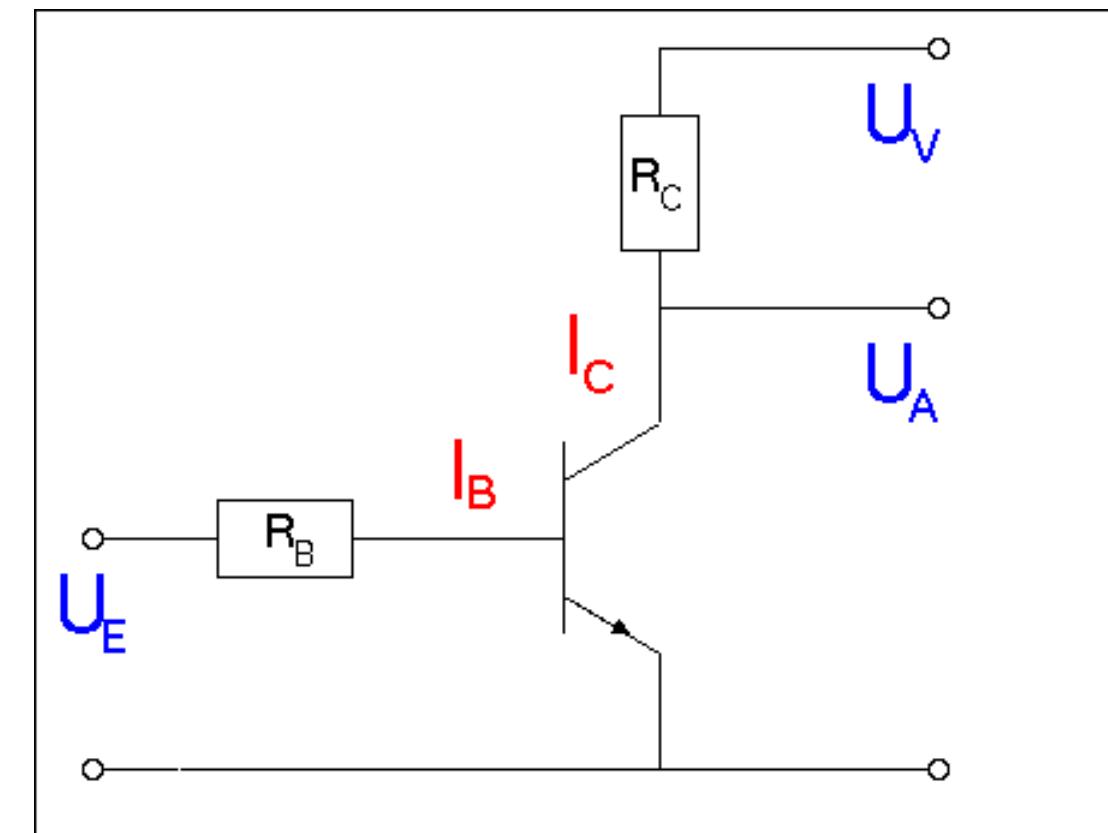

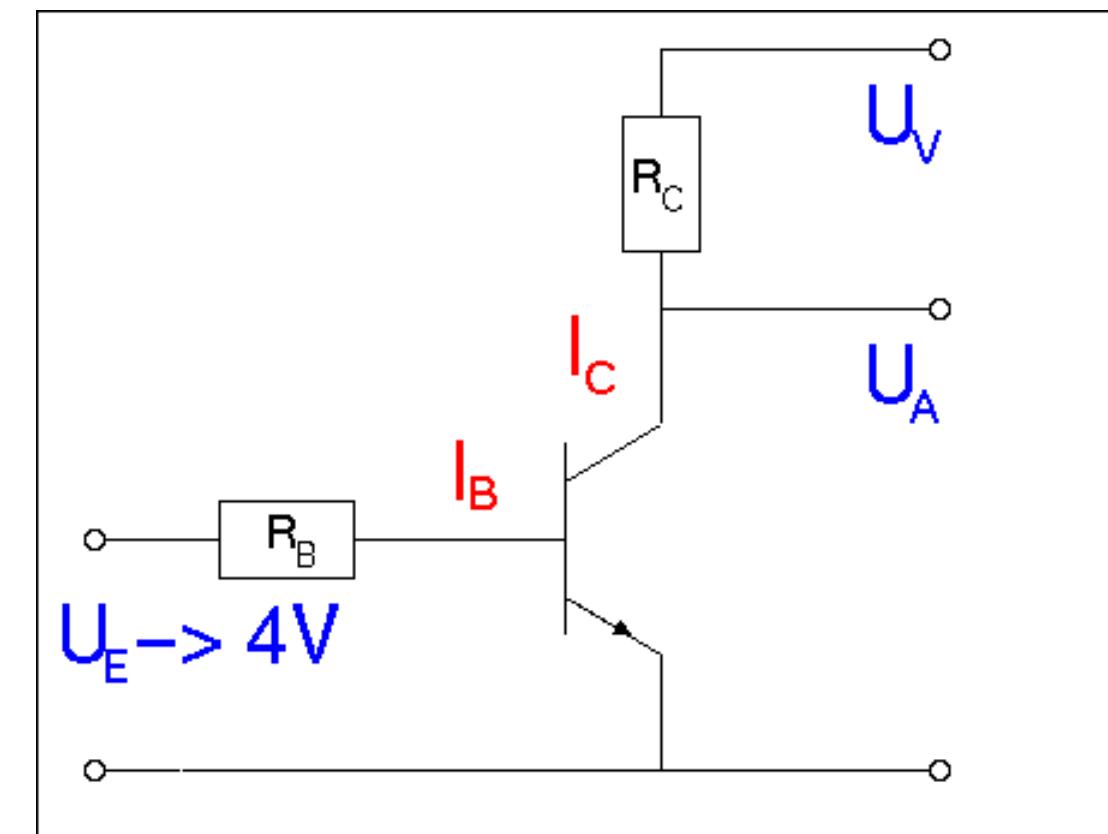

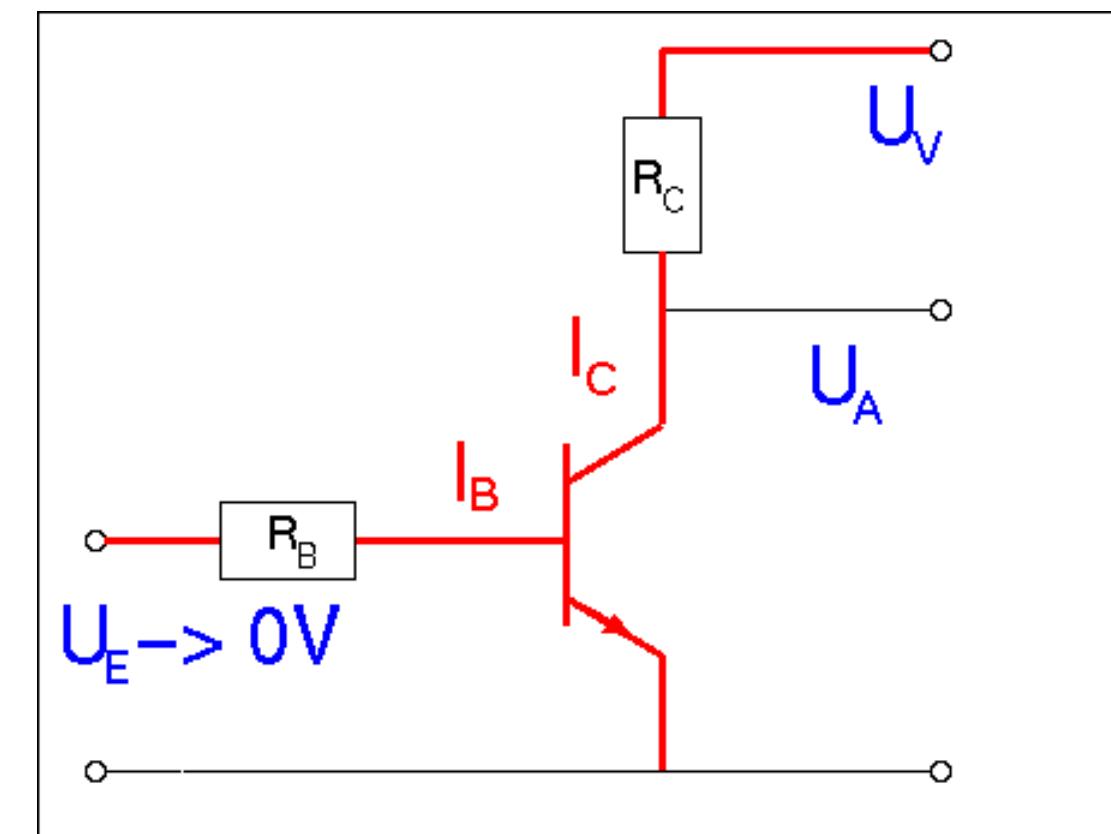

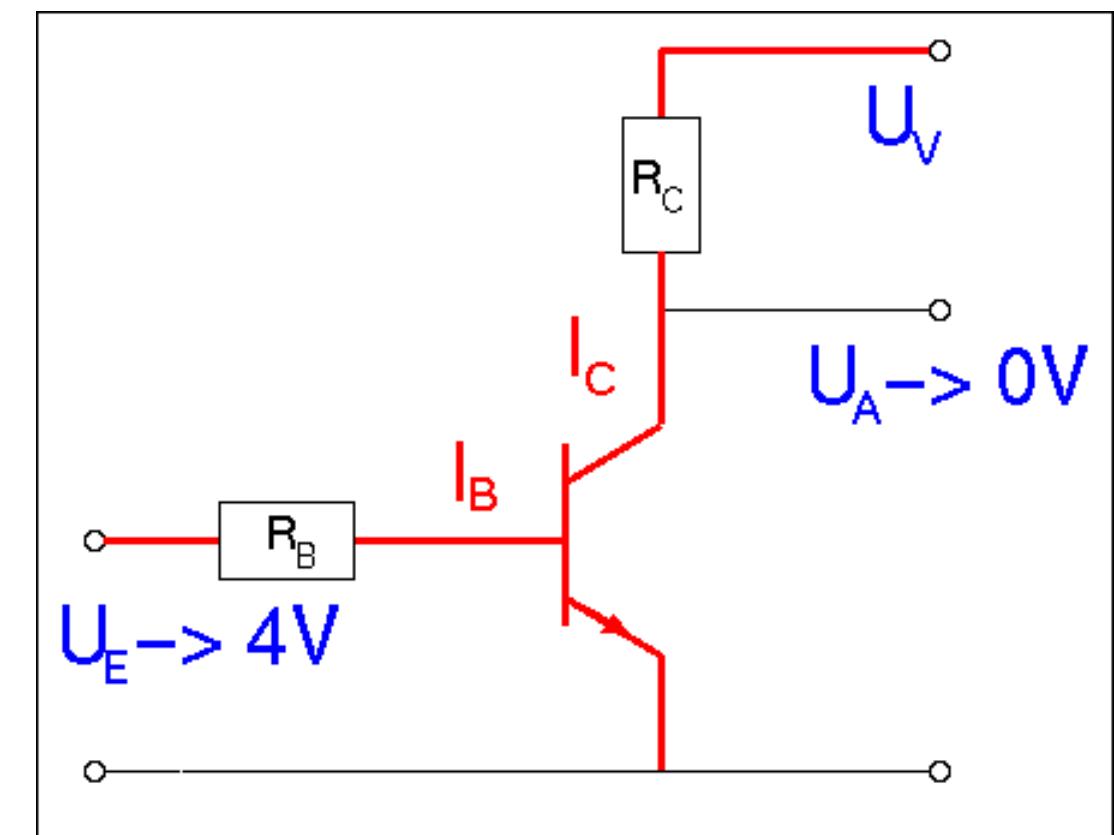

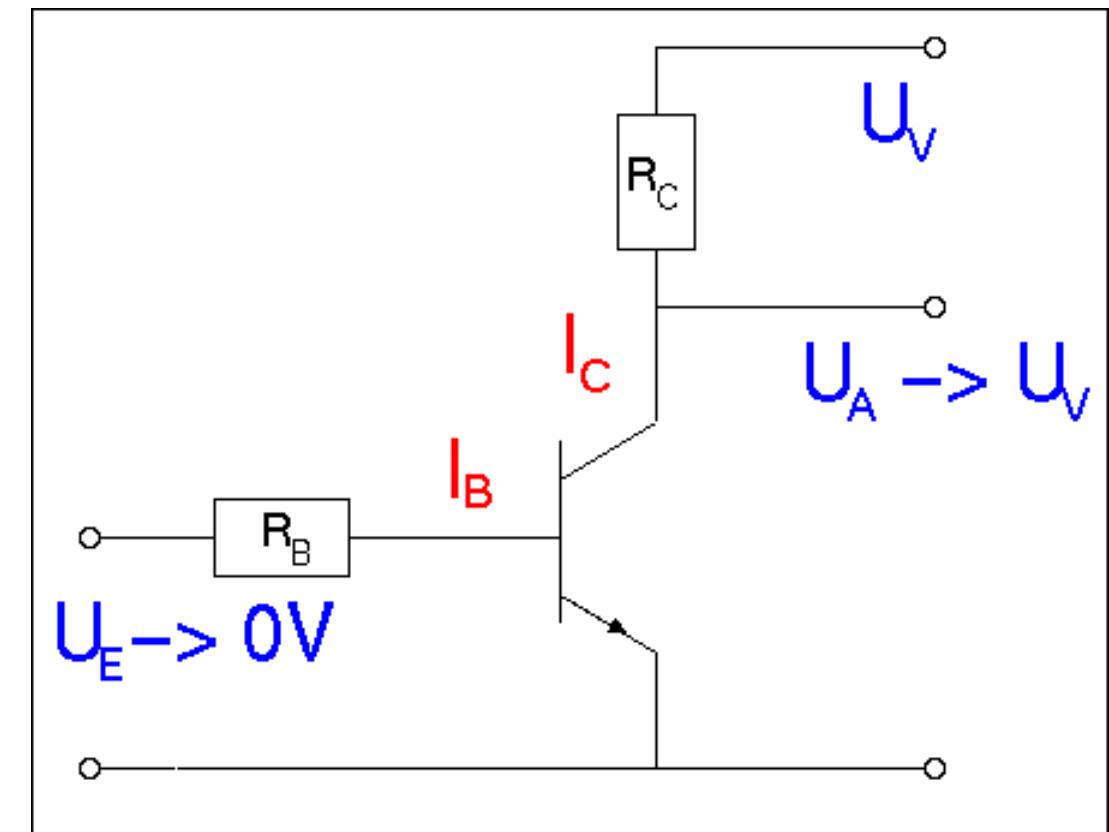

# Transistor als Schalter

Grundschaltung: die Widerstände verhindern Kurzschlüsse

- $U_V$ : Versorgungsspannung

- $U_E$ : Eingangsspannung

- $U_A$ : Ausgangsspannung

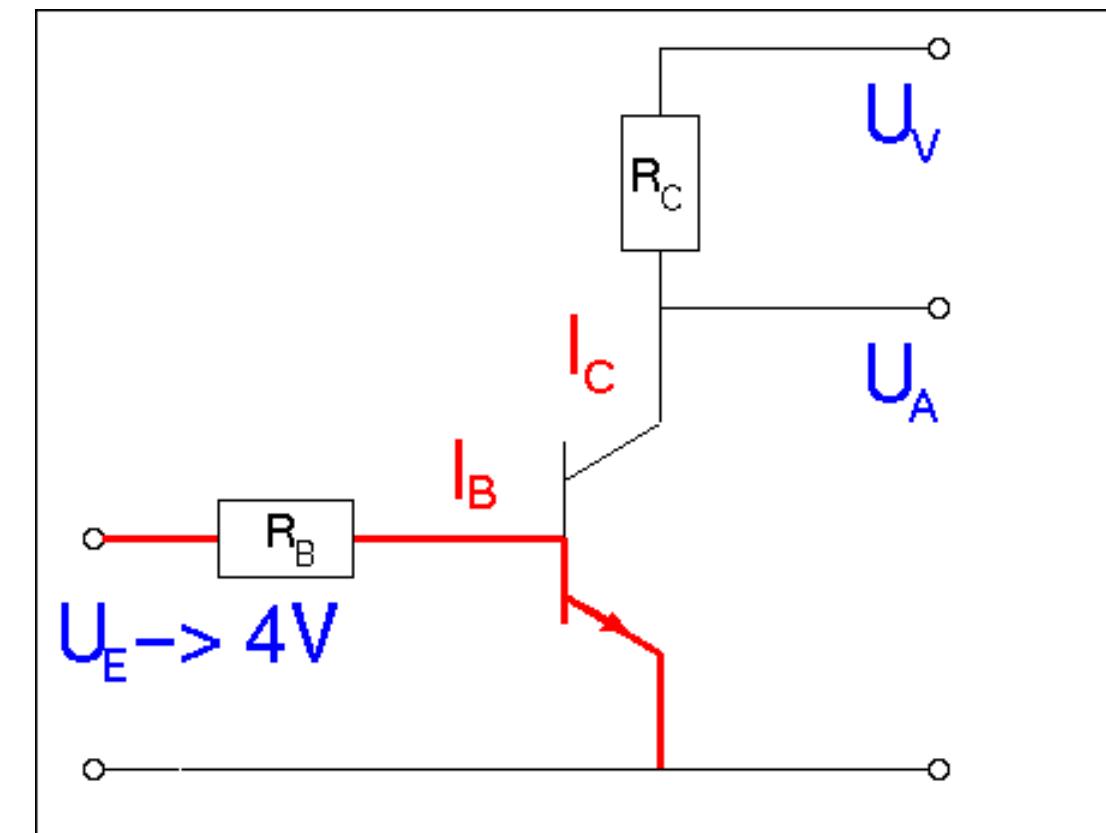

# Geschlossener Schalter

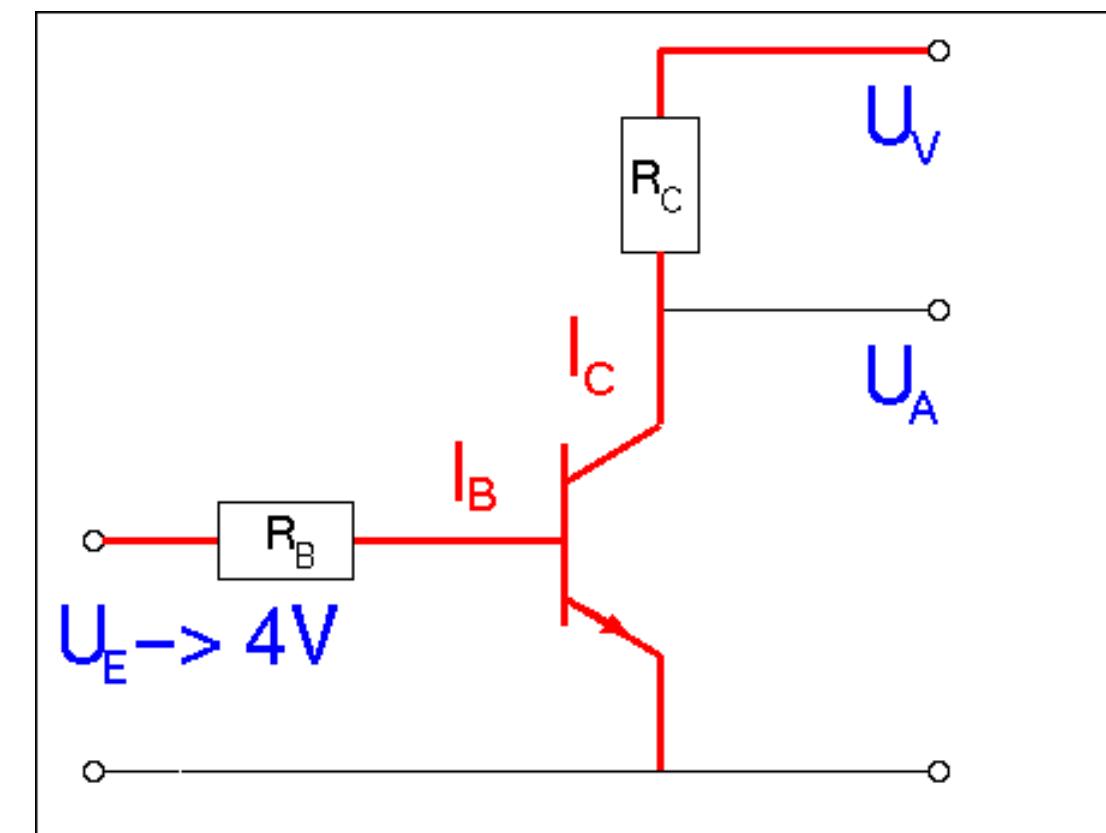

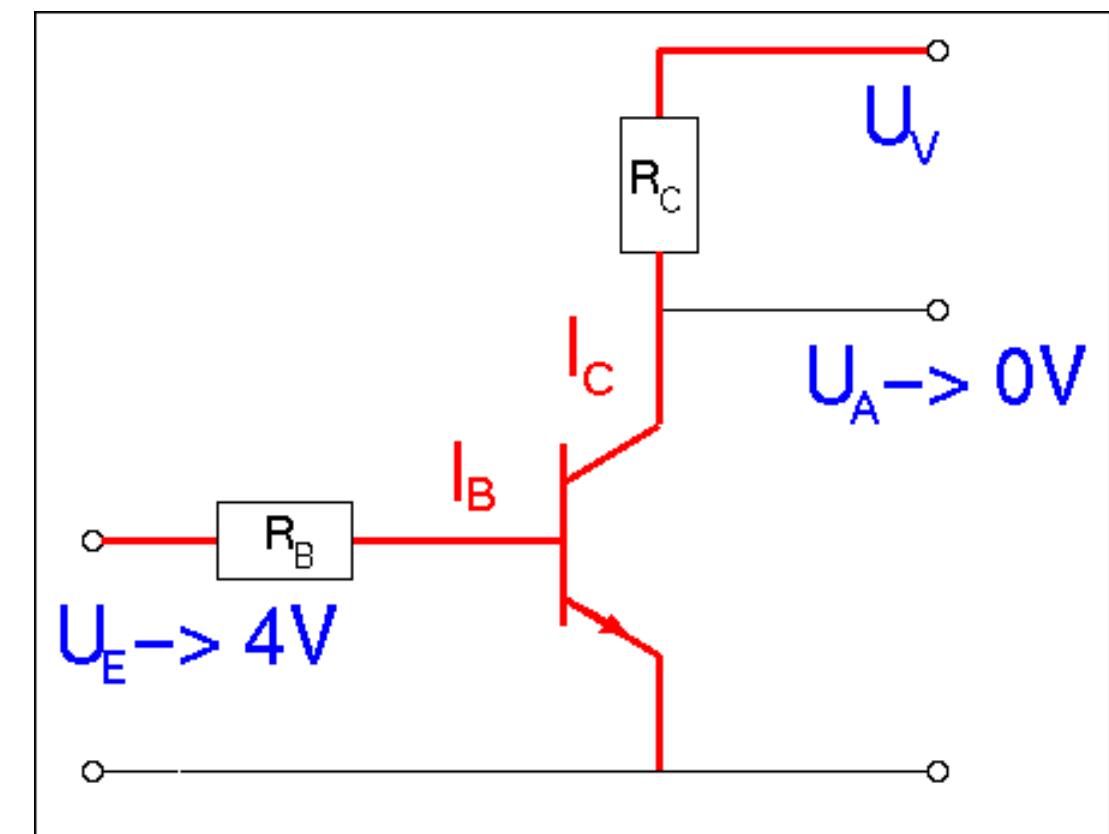

# Geschlossener Schalter

# Geschlossener Schalter

- $I_B = U_E * R_B \rightarrow$  Arbeitspunkt

## Geschlossener Schalter

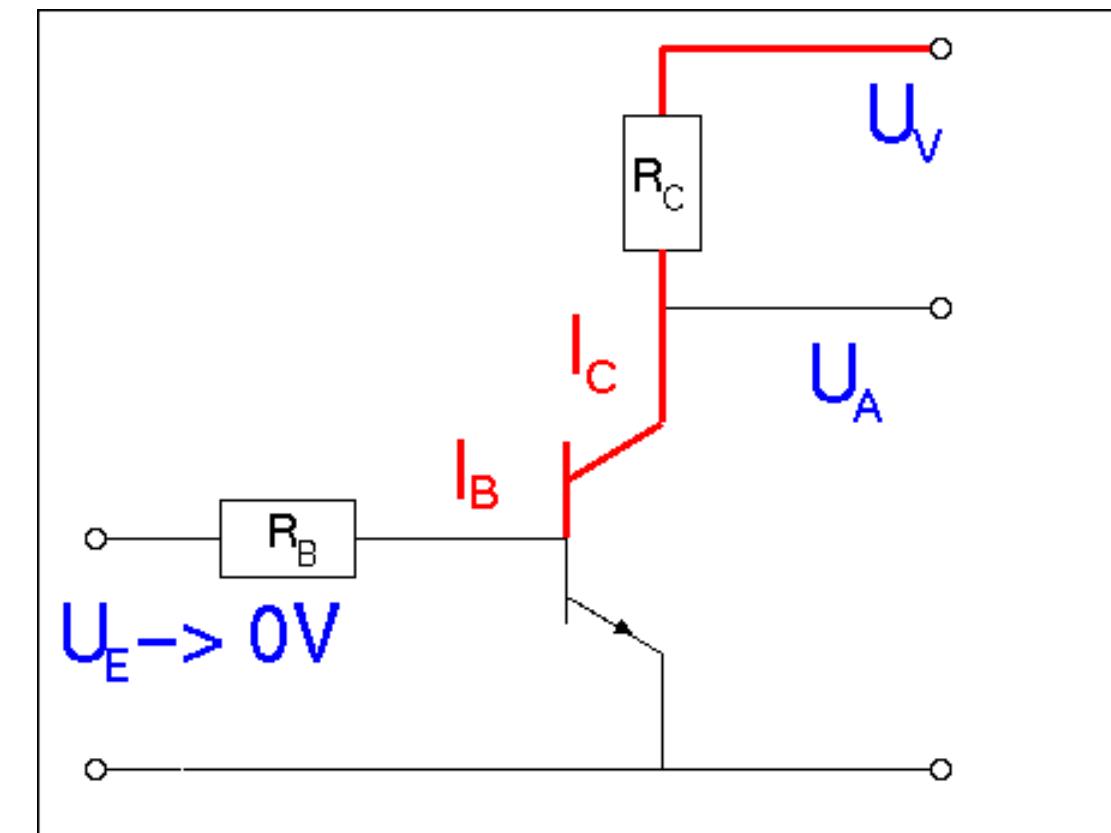

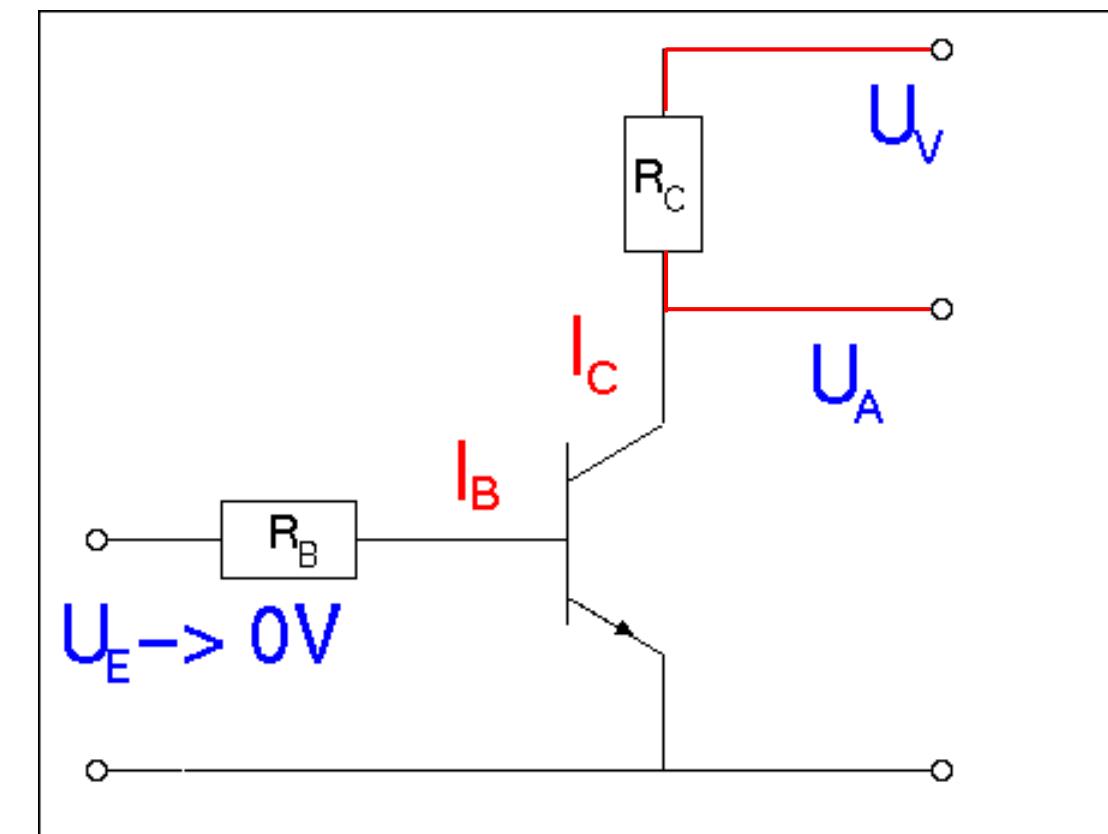

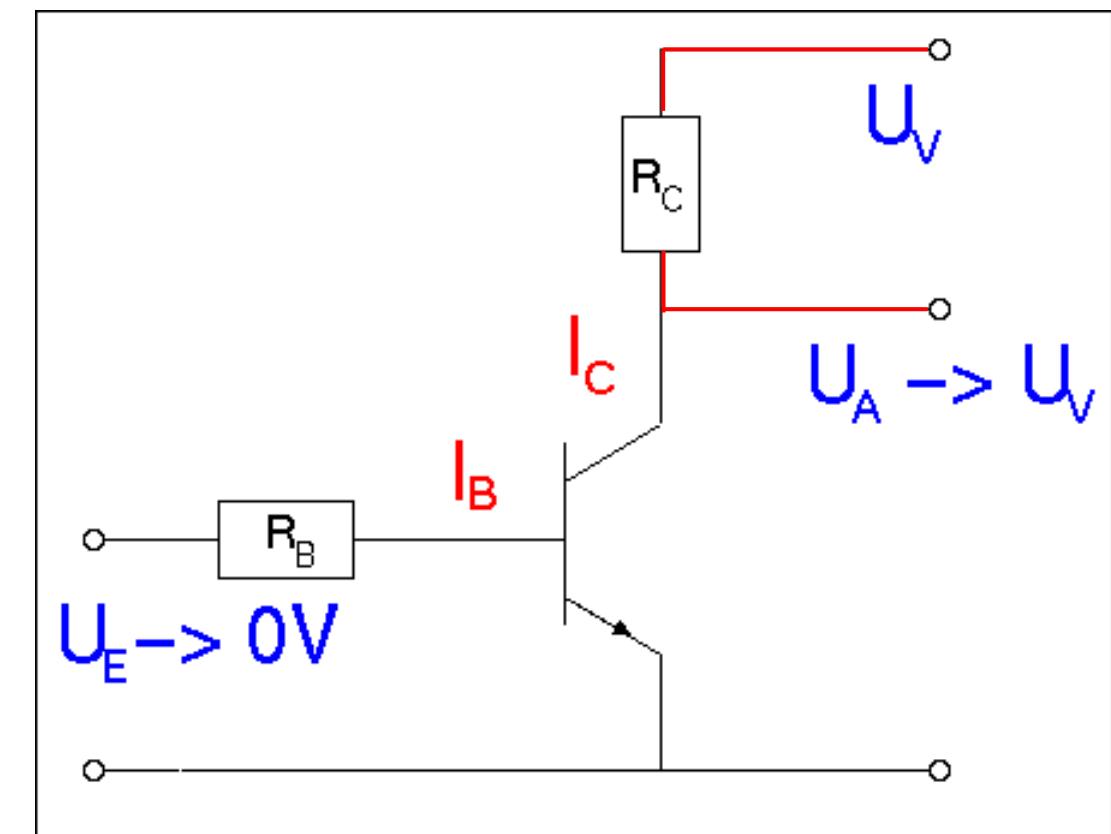

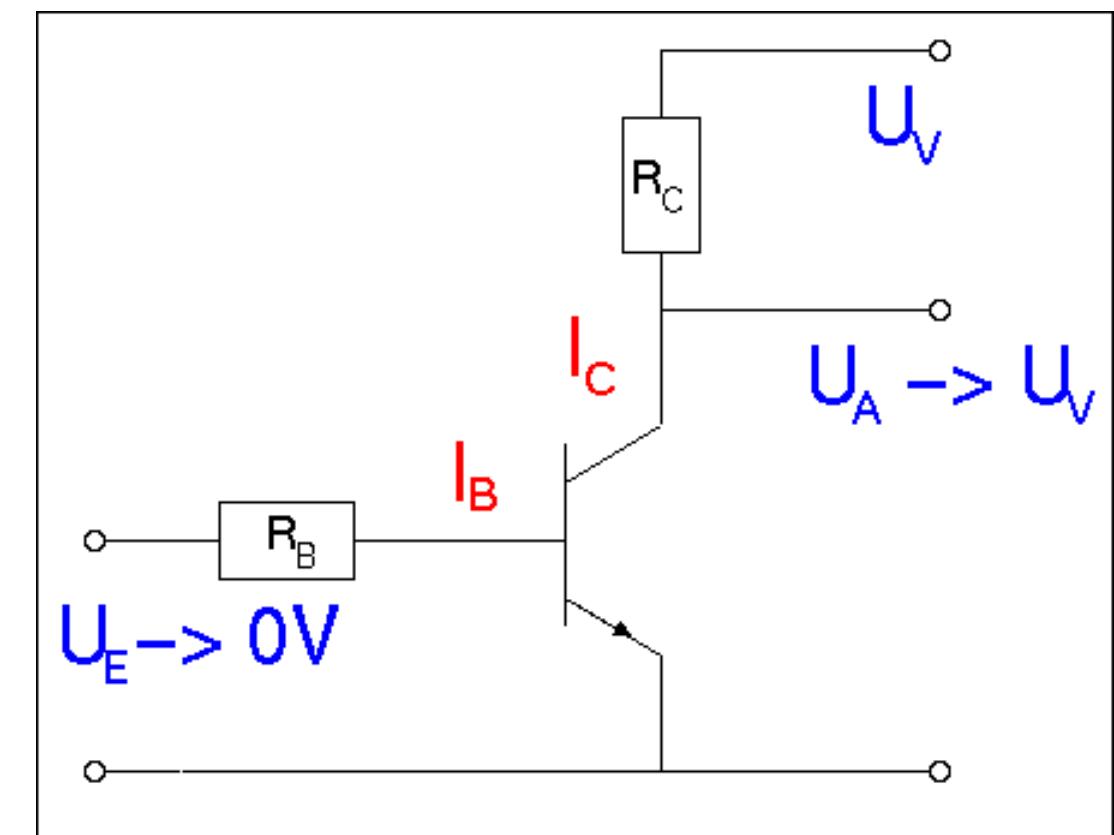

# Offener Schalter

# Offener Schalter

# Offener Schalter

# Offener Schalter

# Kapitel 12: Realisierung digitaler Bausteine

Transistoren

Logische Gatter

Flip Flops

1-Bit Speicherzelle

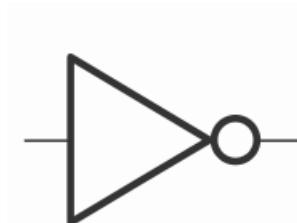

# Invertierendes Gatter

# Invertierendes Gatter

## Invertierendes Gatter

- Interpretation der Spannung:

- $U > U_V - \delta$  heißt logisch „1“

- $U < 0V + \delta$  heißt logisch „0“

- Damit ergibt sich aus der vorherigen Schaltung die folgende Wahrheitstabelle:

| $U_E$ | $U_A$ |

|-------|-------|

| „0“   | „1“   |

| „1“   | „0“   |

- Schaltsymbol:

## AND-Gatter (1)

- Verwendung von Multi-Emitter-Transistoren

- Sobald die Spannung zwischen mindestens einem Emitter und der Basis negativ ist, sperrt der Transistor

## Exkurs: Multi-Emitter-Transistor

*Ein einziger aktiver Emitter genügt, um den „Sprung“ in den n-dotierten Kollektorbereich zu schaffen*

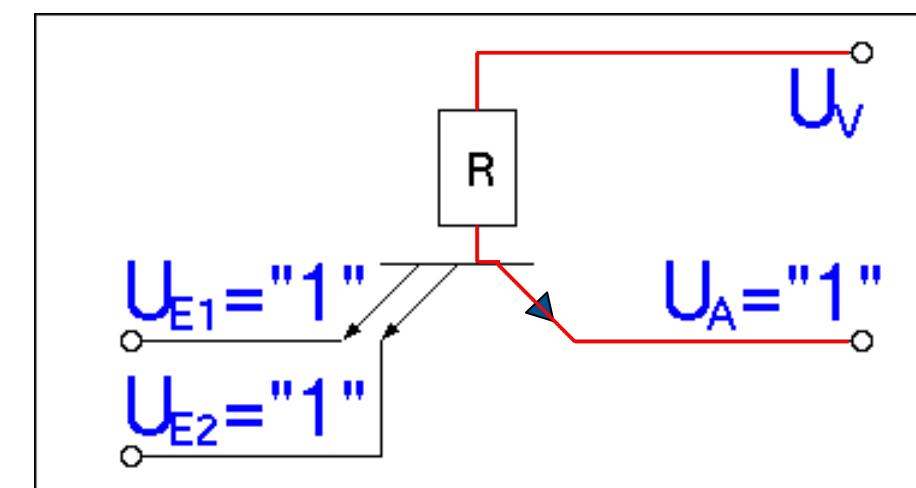

## AND-Gatter (2)

- Beide Eingänge „1“ → Ausgangswert „1“

- Beide Eingänge liegen auf logisch „1“

- Die Spannung zwischen B und E ist 0

- $U_A$  liegt auf logisch „1“

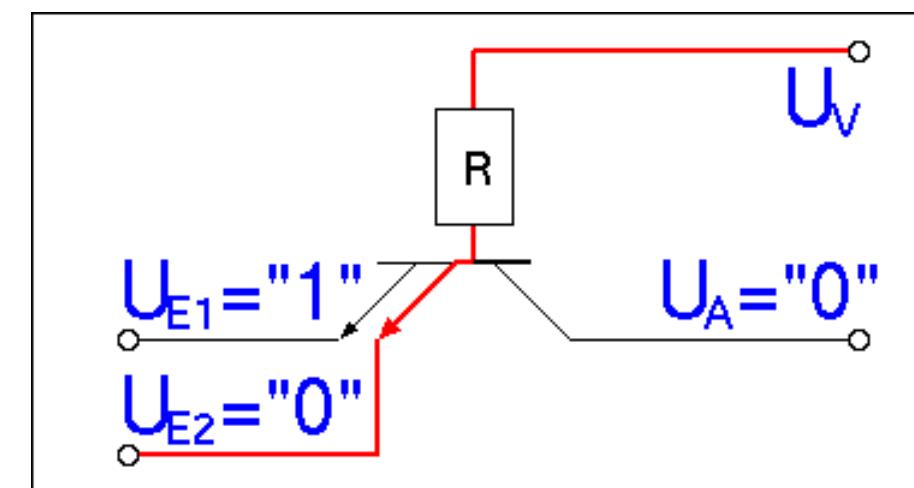

## AND-Gatter (3)

- Mindestens ein Eingang „0“ → Ausgangswert „0“

- Mind. ein Eingang liegt auf logisch „0“

- $U_V$  liegt zwischen B und E an

- $U_A$  wird auf logisch „0“ gezogen

## AND-Gatter (4)

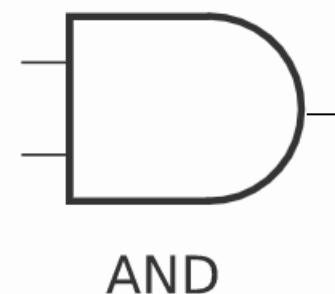

- Das dargestellte Gatter führt eine logische UND-Verknüpfung aus

- In der Praxis wird es aber nur als Eingangsstufe verwendet, eine nachgeschaltete invertierende Endstufe dient zur Leistungssteigerung

- **Schaltsymbol (MIL/ANSI):**

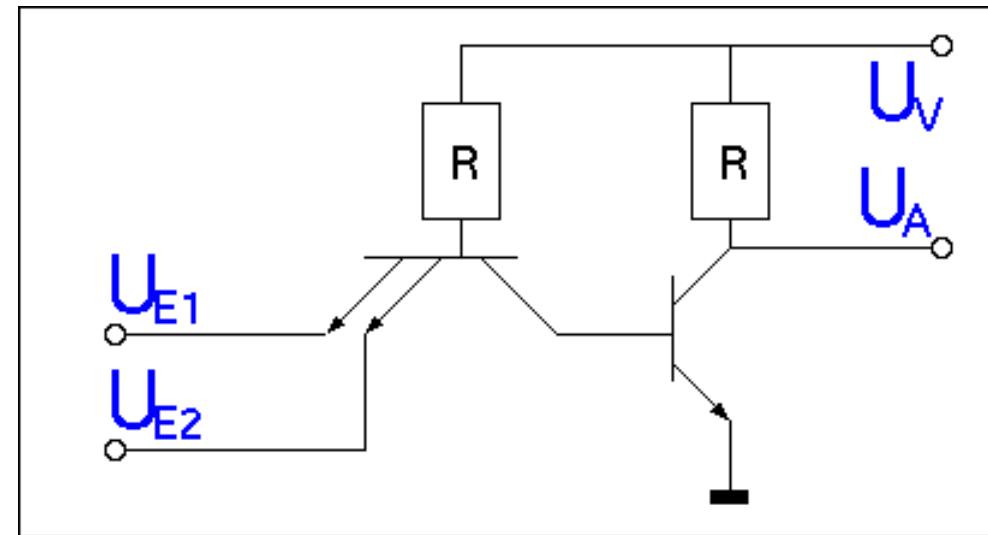

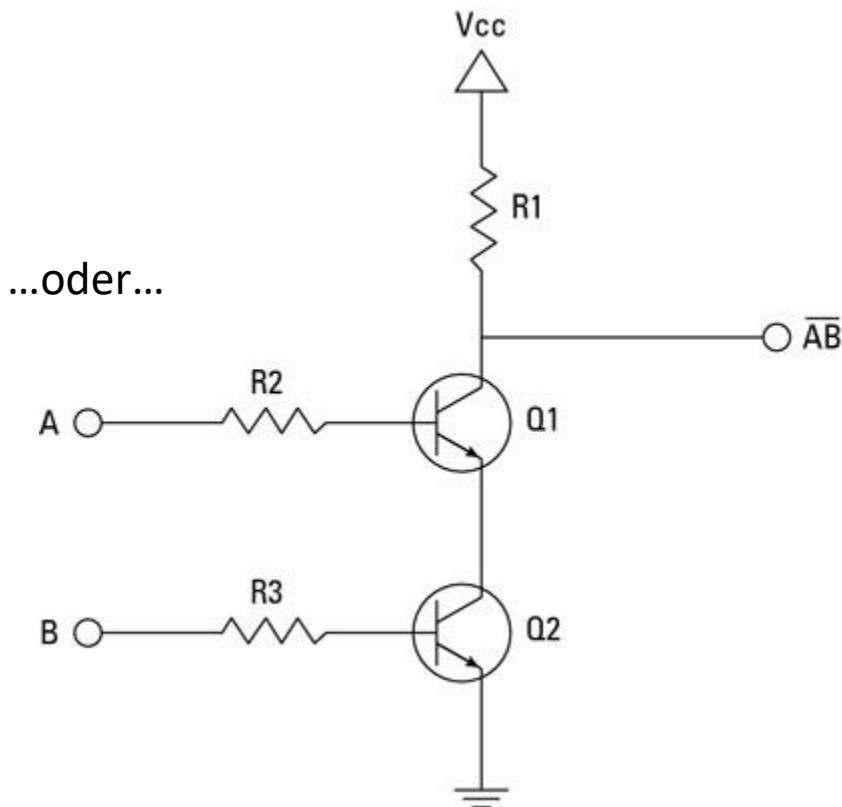

## NAND-Gatter (1)

- Das NAND-Gatter besteht aus dem gezeigten AND-Gatter als Eingangsstufe und einem invertierenden Ausgang

- Schaltsymbol:

...oder...

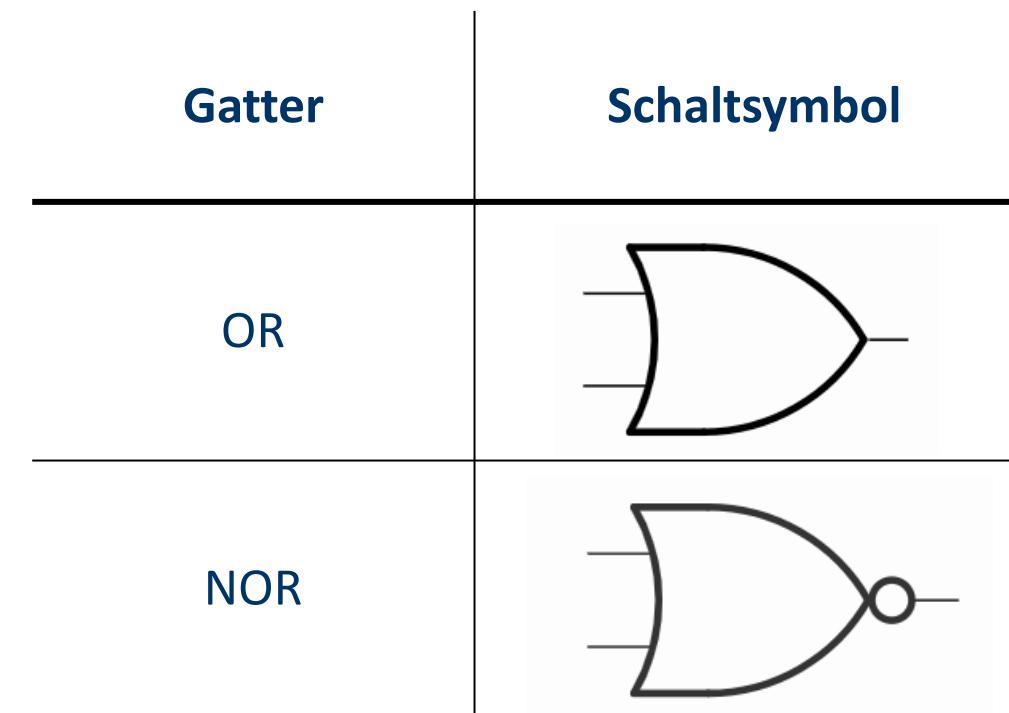

## OR- und NOR-Gatter

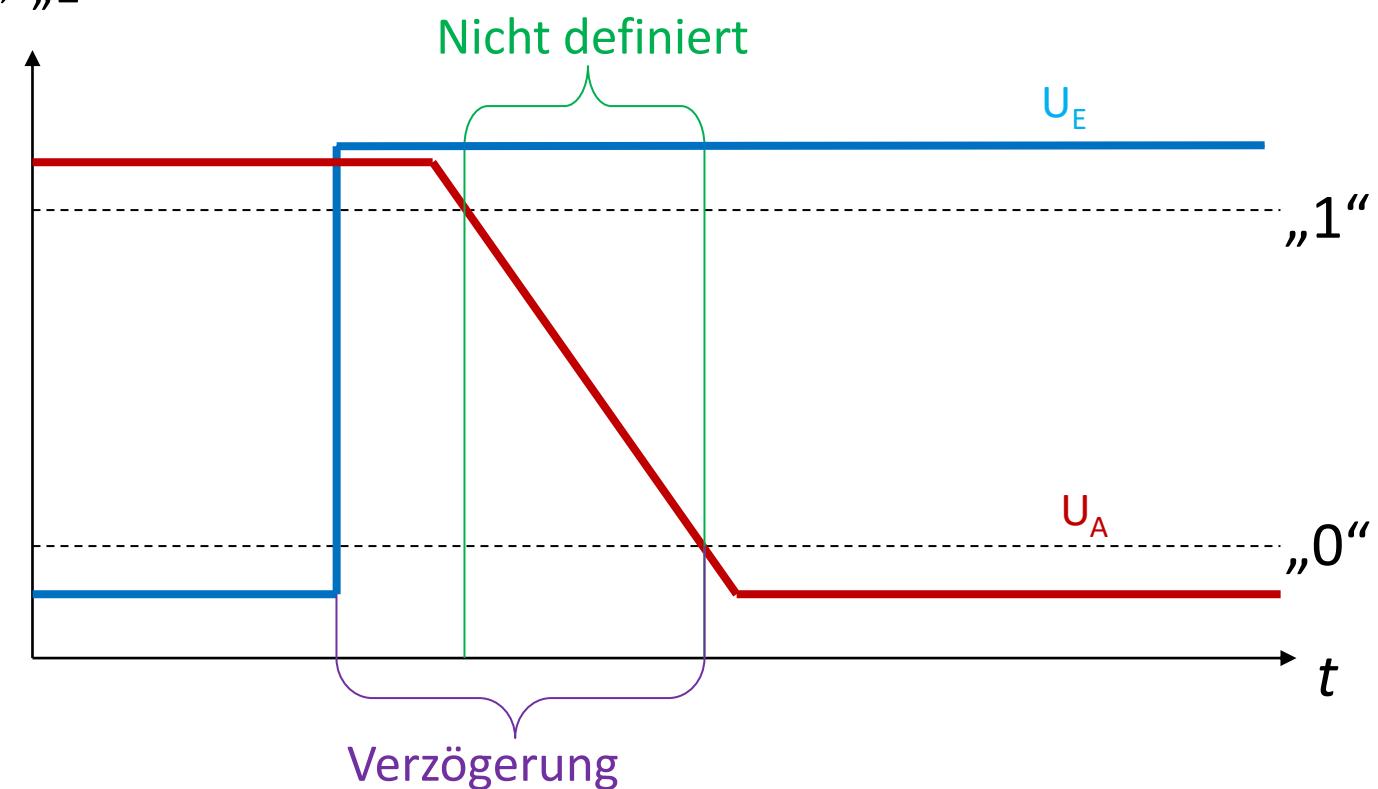

# Physikalische Eigenschaften (1)

- Kein Gatterausgang schaltet verzögerungsfrei

- Der Übergang des Ausgangs von logisch „0“ → „1“ („1“ → „0“) ist nicht unmittelbar

- Beispiel: NOT

## Physikalische Eigenschaften (2)

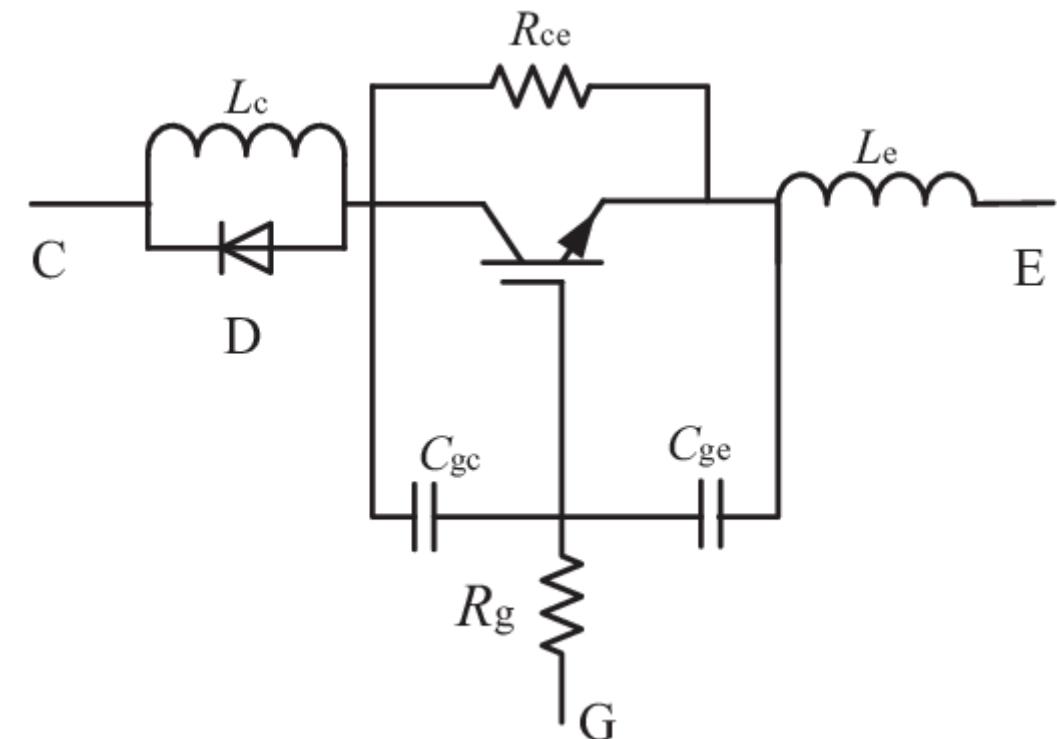

- Parasitäre Induktivitäten und Kapazitäten müssen geladen / entladen werden

- Höhere Frequenz -> Höhere Verluste

- Übersprechen von benachbarten Leitungen

- Bei Gigahertz-Taktraten:

- Ausbreitungsgeschwindigkeit der Elektronen!

$c = 300\ 000 \text{ km/s}$  im Vakuum

- $f = 3 \text{ GHz}$

- 1 Takt -> Licht kommt 30 cm weit...