kap4-1-speicherorganisation-1.pdf

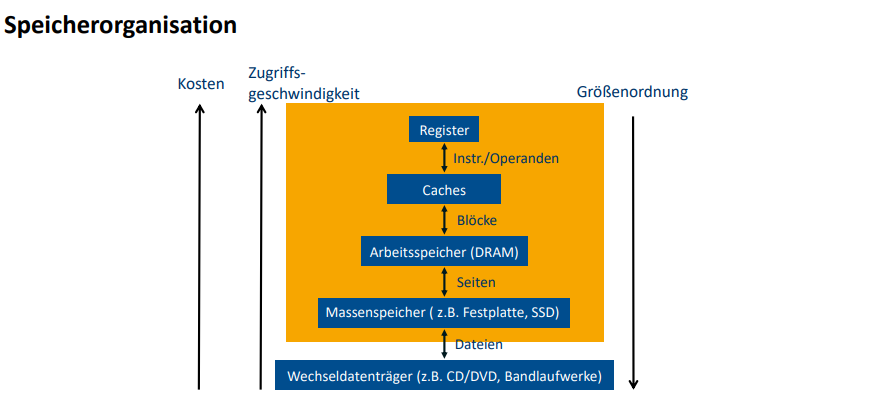

Caches

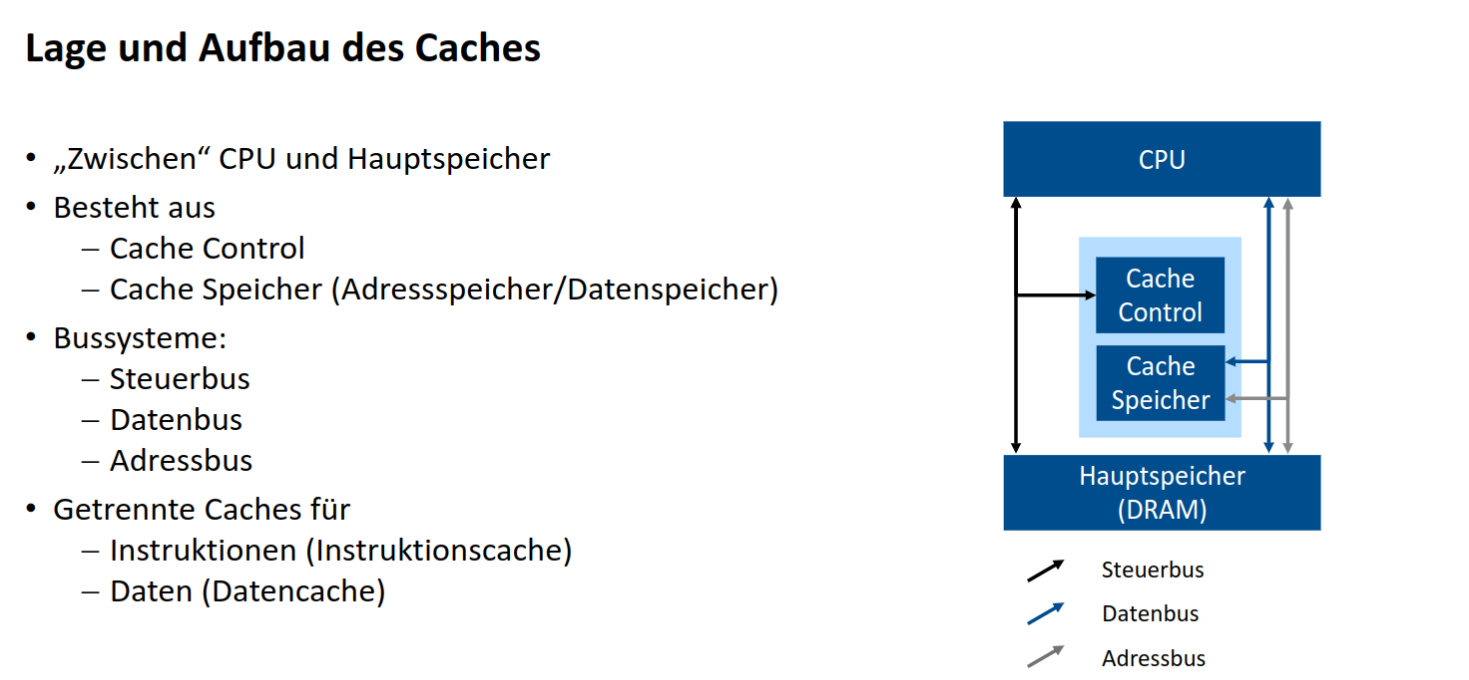

Aufbau

Cach Lesen

CPU überprüft, ob eine Kopie der Hauptspeicherzelle mit Adresse a im Cache abgelegt ist:

cach hit

Daten sind in Cach.

In einem Cycle:

- Läd Cach zu CPU

Zugriffszeit:

Link to originalcach miss

Daten nicht in Cach.

In einem Cycle:

- Läd vom Hauptspeicher in den Cach

- Läd vom Hauptspeicher in die CPU

Zugriffszeit:

Link to originalTrefferate:

Durchschnittliche Zugriffszeit:Schreibzugriff Verfahren

Write trough

Hauptspeicher wird immer aktualisiert

Link to original

- cach miss:

- CPU schreibt Daten in Hauptspeicher

- cach hit:

- Hauptspeicher wird aktualisiert

- Kopie im Cache wird aktualisiert

write back

Hauptspeicher wird aktualisiert wenn aus Cach verdrängt wird.

Link to original

- cach miss

- CPU schreibt in Hauptspeicher

- cach hit

- Kopie wird Cache aktualisiert und mit dirty bit markiert.

- Hauptspeicher wird erst aktualisiert, wenn Kopie aus dem Cache verdrängt wird.

write-allocation

Alles wird erst im Cache behandelt.

Link to original

- cach miss

- CPU schreibt in Cache und makiert mit dirty bit.

- Hauptspeicher wird erst aktualisiert, wenn Kopie aus dem Cache verdrängt wird.

- cach hit

- Kopie wird Cache aktualisiert und mit dirty bit markiert.

- Hauptspeicher wird erst aktualisiert, wenn Kopie aus dem Cache verdrängt wird.

DMA

Direct Access Memory Controller

Erlaubt das man direckt mir dem Hauptspeicher komunizieren.

Disk zu RAM ohne das die CPU Involviert ist.

Link to originalVerdrängungs Stratigie

FIFO

First in First out.

Einfach immer push back und pop front.

Link to originalLFU

Least frequently used

Was am wenigstens gelesen wird fliegt raus.

Link to originalLRU

Least recently used

Was am längsent nicht benutzt wurde fliegt raus.

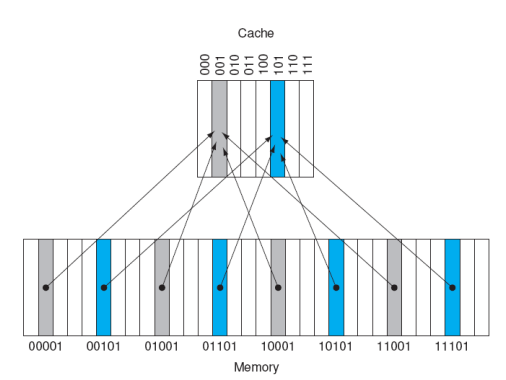

Link to originalDirect Mapped Cache

Die letzten paar bits der Hauptspeicher Adresse stehen für Cach Adresse

Cach Adresse = Hauptspeicher Adresse % Cachgröße

Cache Tag

Die restlichen Bits der Hauptspeicher Adresse

Valid Bit

Gibt an ob der eintrag gültig ist.

Wichtig

Keine Verdrenungsstratigie benötigt.

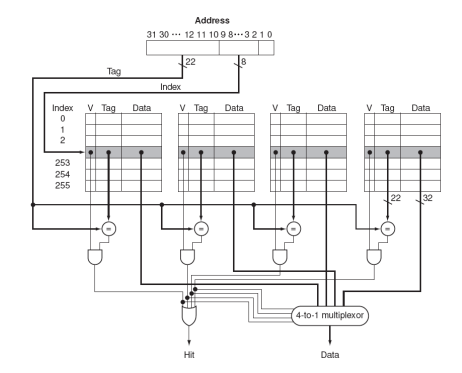

Link to originalLink to originalDMC

Direct Mapped Cache UND Assoziativer Cache

mehere parallele Direct Mapped Caches in einem Assoziativen Cache

Link to original

Massen speicher

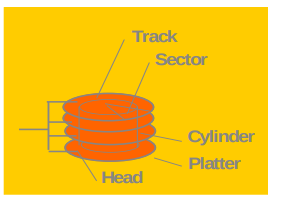

HDD

- Eine Festplatte besteht aus

- mehreren Platten (4-8)

- mehreren Lese-/Schreibköpfen (4-16)

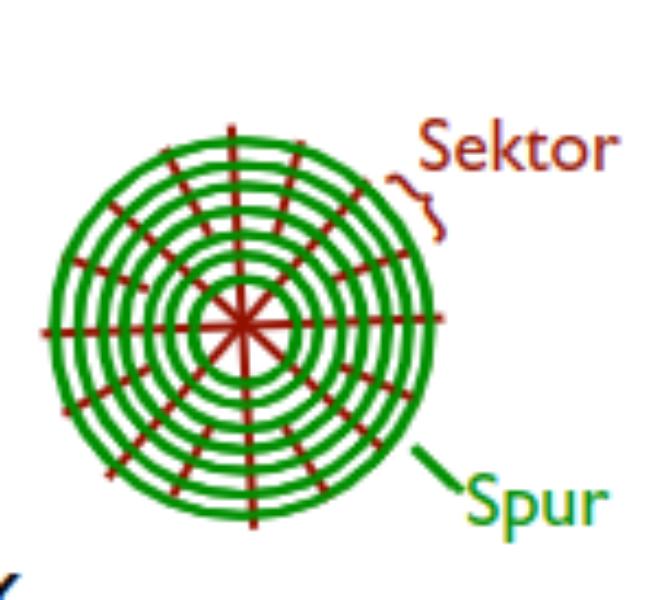

- Eine Platte besteht aus konzentrischen Spuren

- Eine Spur besteht aus Sektoren

- Ein Sektor ist die kleinste beschreibbare Einheit

- Ein Zylinder besteht aus übereinanderliegenden Spuren

Früher waren alle Köpfe immer an der gleichen Position daher liest man immer einen Zylinder.

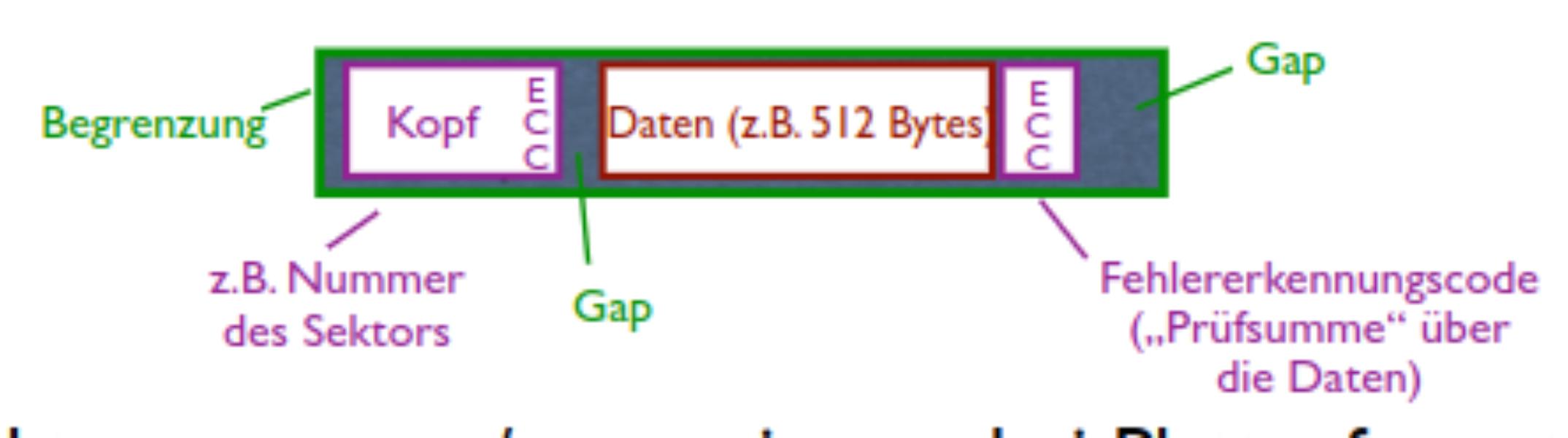

Heute kann man die Leseköpfe auch unabhängig regulieren.Sektor

Werte

- Rotationsgeschwindigkeit: 3.600 rpm bis 10.800 rpm (revolutions per minute)

- Sektorgröße: 128 Byte bis 1 KiB

- Schreibdichte: 50.000 bis 270.000 Bits/cm

- Spurendichte: 800 bis 10.000 Spuren/cm

Zugriff auf Datenblock x

- Oberfläche i, Spur j, Sektor k

- Positionieren des Arms auf Spur j

- Warten bis Platte auf Sektor k gedreht wurde

- Aktivieren des Schreib-/Lesekopfs von Oberfläche i

Verfahren zur Positionierung des Arms

- Schrittmotor: langsam, veraltet

- Servo-Oberfläche: Grobpositionierung durch Impuls und eigene Oberfläche mit Infos zur Nachregulierung

⇒ ungerade Anzahl von „Nutz“-Oberflächen- Nachregulierungsinfos auf jeder Oberfläche (heute üblich)

⇒ Schreib-/Leseköpfe unabhängig regulierbarshiehe auch: Zugriffsalgorithmen auf Plattenblöcke

Zugriffszeit

Bewege die Köpfe zu dem richtigen Zylinder (Dauer: ca. 10 ms)

Warte, bis der gesuchte Sektor zum Kopf rotiert (Dauer: 0.5 * Rotation)

Übertrage den Inhalt des Sektors (Transferrate: 20-100 MB/s)

siehe auch:

Link to original

HDD Desing Auswirkung auf Dateisysteme

Fehlerhafte Plattenblöcke

HDD Blockgröße

SSD